Daftar Isi:

- Langkah 1: Tambahkan Sumber dan Pilih “Tambah atau Buat Sumber Simulasi

- Langkah 2: Buat File Bernama Enable_sr_tb

- Langkah 3: Buat File Testbench

- Langkah 4: Tetapkan Enable_sr_tb Sebagai Tingkat Atas Di Bawah Simulasi

- Langkah 5: Jalankan Sintesis & Simulasi Perilaku

- Langkah 6: Evaluasi Hasil Simulasi

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:57.

- Terakhir diubah 2025-01-23 14:49.

Saya telah melakukan proyek simulasi ini untuk kelas online. Proyek ini ditulis oleh Verilog. Kami akan menggunakan simulasi di Vivado untuk memvisualisasikan bentuk gelombang di enable_sr(enable digit) dari proyek stop watch yang dibuat sebelumnya. Selain itu, kami akan menggunakan tugas sistem untuk menampilkan kesalahan yang kami buat dalam desain.

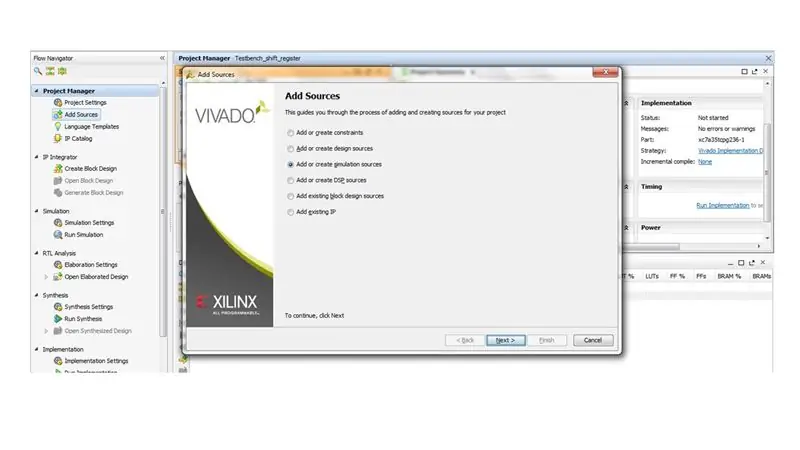

Langkah 1: Tambahkan Sumber dan Pilih “Tambah atau Buat Sumber Simulasi

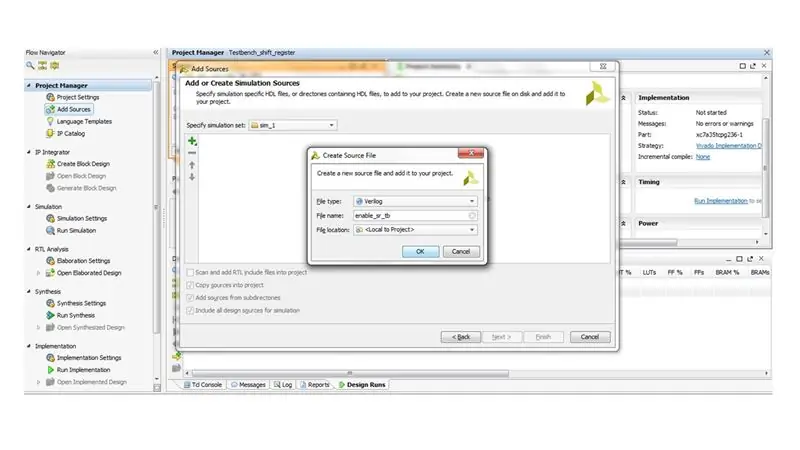

Langkah 2: Buat File Bernama Enable_sr_tb

Langkah 3: Buat File Testbench

1. Impor modul enable_sr dari proyek stop watch. Itu adalah file yang ingin kami simulasikan

2. Buat modul testbench enable_sr_tb();

3. Masukkan input dan output modul enable_sr(). Ingat input untuk enable_sr sekarang dalam tipe register sedangkan output menjadi tipe net.

4. Instansiasi unit yang sedang diuji (uut) yang merupakan enable_sr

5. Hasilkan jam dengan periode (T) 20ns

6. Gunakan pernyataan kondisional untuk membuat sistem pengecekan kesalahan. Dalam contoh ini, kami ingin memeriksa apakah ada lebih dari satu digit yang aktif.

Catatan: Dalam file enable_sr() asli, kita harus menginisialisasi pola sebagai 4'b0011 sehingga ada dua digit yang aktif untuk membuat kesalahan

7. Gunakan tugas sistem $display untuk menunjukkan kesalahan

8. Gunakan tugas sistem $selesai untuk menyelesaikan simulasi pada waktu 400ns

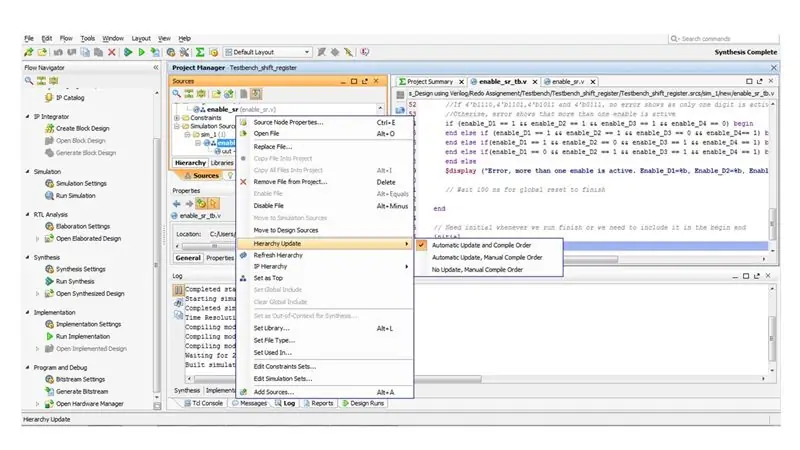

Langkah 4: Tetapkan Enable_sr_tb Sebagai Tingkat Atas Di Bawah Simulasi

Langkah 5: Jalankan Sintesis & Simulasi Perilaku

- Sebelum menjalankan simulasi perilaku, jalankan sintesis untuk memastikan tidak ada kesalahan sintaks pada file testbench dan unit di bawah file pengujian

- Jalankan simulasi perilaku

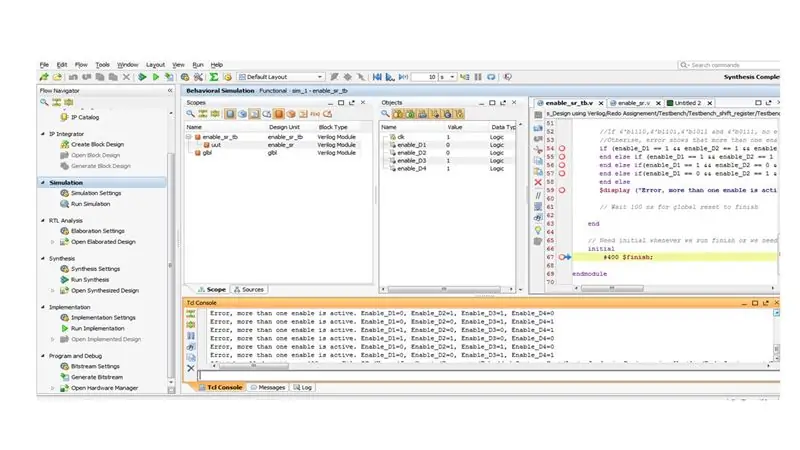

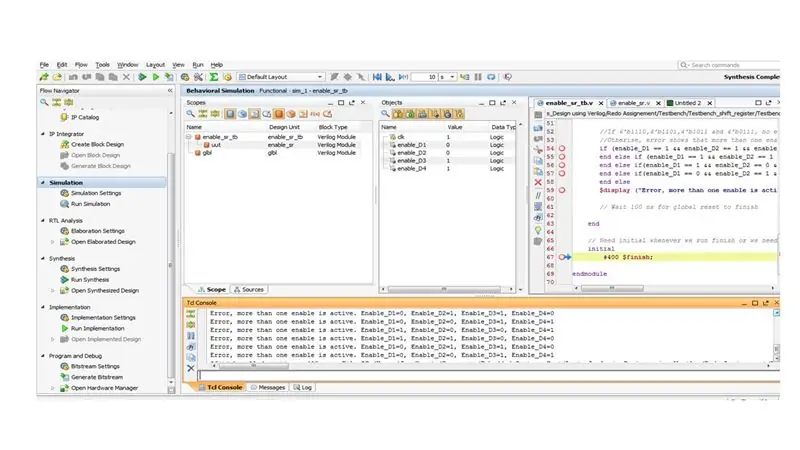

Langkah 6: Evaluasi Hasil Simulasi

Anda akan melihat jendela simulasi. Ini berisi panel yang berbeda.

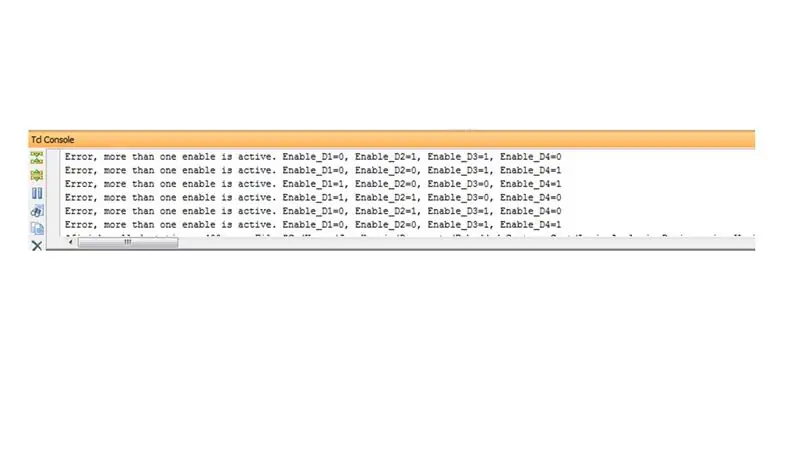

Anda akan melihat pesan kesalahan di panel konsol. Ini menunjukkan lebih dari satu digit aktif selama periode simulasi.

Anda juga dapat melihat bentuk gelombang di ruang lingkup

Terlampir adalah file proyek.

Direkomendasikan:

Simulasi Akuisisi Sinyal EKG Menggunakan LTSpice: 7 Langkah

Simulasi Akuisisi Sinyal EKG Menggunakan LTSpice: Kemampuan jantung untuk memompa adalah fungsi dari sinyal listrik. Dokter dapat membaca sinyal-sinyal ini pada EKG untuk mendiagnosis berbagai masalah jantung. Namun, sebelum sinyal dapat disiapkan dengan baik oleh dokter, sinyal tersebut harus disaring dan diperkuat dengan

EKG Otomatis: Simulasi Amplifikasi dan Filter Menggunakan LTspice: 5 Langkah

EKG Otomatis: Simulasi Amplifikasi dan Filter Menggunakan LTspice: Ini adalah gambar perangkat terakhir yang akan Anda buat dan diskusi yang sangat mendalam tentang setiap bagian. Juga menjelaskan perhitungan untuk setiap tahap.Gambar menunjukkan diagram blok untuk perangkat iniMetode dan Bahan: Tujuan dari latihan ini

SIMULASI MESIN DESINFEKSI MENGGUNAKAN TINKERCAD: 6 Langkah

SIMULASI MESIN DESINFEKSI MENGGUNAKAN TINKERCAD: Dalam pembahasan ini kita akan melihat bagaimana membuat simulasi Mesin Disinfeksi,Contact less Automatic Sanitizer adalah mesin desinfeksi karena kita tidak akan menggunakan tangan kita untuk mengoperasikan mesin melainkan sensor inframerah Proximity merasakan ou

Simulasi Open Loop Opamp Menggunakan Aplikasi EveryCiruit: 5 Langkah

Simulasi Open Loop Opamp Menggunakan Aplikasi EveryCiruit: EveryCircuit adalah salah satu platform simulasi 'terbaik' untuk elektronik. Ini memiliki situs web dan Aplikasi. Instruksi ini untuk versi Android. Tetapi persis mengikuti untuk versi web juga. Tentang Instruksi ini: Opamp atau Penguat Operasional adalah

(LED With Switch) Simulasi Arduino Menggunakan Sirkuit Tinkercad: 5 Langkah

(LED With Switch) Simulasi Arduino Menggunakan Sirkuit Tinkercad: Kami adalah sekelompok mahasiswa UQD0801(Robocon 1) dari Universiti Tun Hussein Onn Malaysia (UTHM) yang akan mendemonstrasikan cara mensimulasikan LED dengan sakelar menggunakan Arduino dan beberapa komponen sebagai bagian dari tugas kami. Oleh karena itu, kami akan memperkenalkan b