Daftar Isi:

- Langkah 1: Membangun Modul PWM- File Sumber

- Langkah 2: Membangun Modul PWM- Pengaturan Vivado

- Langkah 3: Membangun Modul PWM- Buat File Proyek

- Langkah 4: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (I)

- Langkah 5: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (II)

- Langkah 6: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (III)

- Langkah 7: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (IV)

- Langkah 8: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (V)

- Langkah 9: Membangun Modul PWM- Instalasi Perangkat Keras

- Langkah 10: Membangun Modul PWM- Hasilkan Bitstream dan Luncurkan SDK

- Langkah 11: Membangun Modul PWM- Buat Aplikasi Baru di Xilinx SDK

- Langkah 12: Membangun Modul PWM- Gambaran Umum Project Explorer (I)

- Langkah 13: Membangun Modul PWM- Gambaran Umum Project Explorer (II)

- Langkah 14: Membangun Modul PWM- Tinjauan Proyek Explorer (III)

- Langkah 15: Membangun Modul PWM- Membungkus Fungsi PWM (I)

- Langkah 16: Membangun Modul PWM- Membungkus Fungsi PWM (II)

- Langkah 17: Membangun Modul PWM- Membungkus Fungsi PWM (III)

- Langkah 18: Membangun Modul PWM- Jalankan

- Langkah 19: Pemrosesan Video Streaming di Digilent ZYBO Dengan OV7670

- Langkah 20: Diagram Blok Lengkap

- Langkah 21: Hubungkan OV7670 ke ZYBO

- Langkah 22: Buat Desain Blok

- Langkah 23: Tambahkan File VHDL untuk Kontrol dan Tangkap Kamera OV7670

- Langkah 24: Tambahkan File Kendala

- Langkah 25: Tambahkan Repo IP untuk HLS IP

- Langkah 26: Tambahkan Modul dan IP

- Langkah 27: Pengaturan Konfigurasi IP

- Langkah 28: Tambahkan dan Konfigurasi Blok IP PS

- Langkah 29: Bagian 1. Membangun Modul PWM untuk Motor Servo

- Langkah 30: Koneksi Sisi Input Video (aclk Disorot)

- Langkah 31: Koneksi ke OV7670

- Langkah 32: Koneksi di Sisi Luar Video

- Langkah 33: Jalankan Blokir dan Otomatisasi Koneksi

- Langkah 34: Hasilkan Pembungkus HDL

- Langkah 35: Hasilkan Bitstream, Ekspor Perangkat Keras ke SDK, Luncurkan SDK Dari Vivado

- Langkah 36: SDK (tanpa FreeRTOS)

- Langkah 37: Implementasi FreeRTOS

- Langkah 38: Petunjuk Penggunaan

- Langkah 39: Referensi dan Tautan

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:58.

- Terakhir diubah 2025-01-23 14:49.

Mulai dari langkah pertama untuk detail tentang cara membuat pengontrol PWM servo 2-sumbu.

Mulai dari diagram blok masif (Langkah 19) untuk proyek penuh.

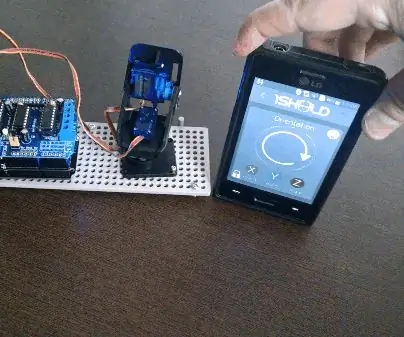

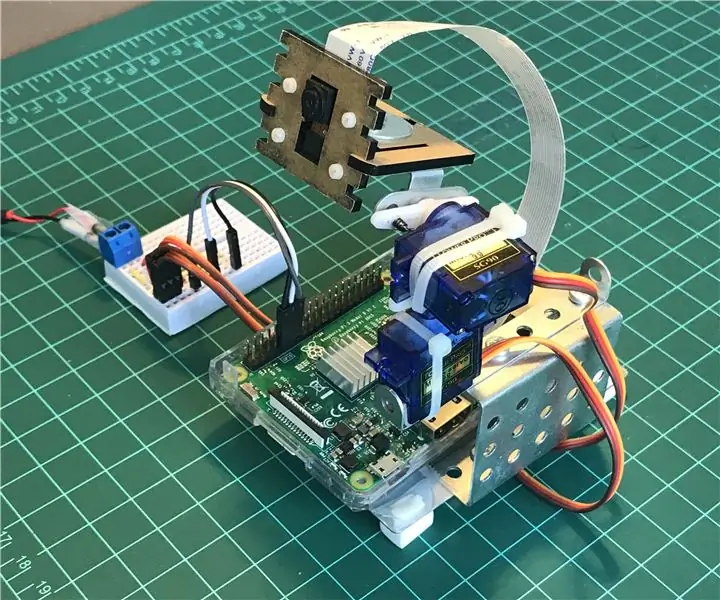

Pengaturan Kamera + Pan/tilt yang kami gunakan:

PmodCON3 dari Digilent digunakan untuk menghubungkan servos.

Langkah 1: Membangun Modul PWM- File Sumber

Langkah 2: Membangun Modul PWM- Pengaturan Vivado

Pertama, unduh Vivado Design Suite Dari situs web Xilinx. Instal semua rangkaian desain, termasuk Vivado Software Development Kit (SDK). Proyek ini menggunakan versi 2017.2.

Sementara itu, Digilent Adept 2 juga harus diinstal sebagai driver papan Zybo.

Langkah 3: Membangun Modul PWM- Buat File Proyek

Sebelum membuat file proyek, Anda harus memastikan bahwa Anda sudah menginstal file Zybo dengan benar seperti tutorial di sini:

Vivado Versi 2015.1 dan Instalasi File Board yang Lebih Baru

Buka Vivado 2017.2. Pada Mulai Cepat, klik Buat Proyek -> Berikutnya -> Nama Proyek (Beri nama proyek Anda di sini) -> Jenis Proyek. Pada Jenis Proyek, pilih Proyek RTL dan tandai "Jangan tentukan sumber saat ini". Selanjutnya, untuk Default Part, pilih “Boards” dan “Zybo” sebagai Display Name. Selanjutnya, Klik Finish untuk memulai proyek.

Langkah 4: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (I)

Pada Flow Navigator, klik “”Create Block Design”, lalu tekan OK. klik tanda “+” untuk menambahkan IP yang diperlukan. Menambahkan:

- Satu Sistem Pemrosesan ZYNQ7 Dua Timer AXI

- Dua Timer AXI

Langkah 5: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (II)

Setelah Menambahkan IP, Jalankan Block Automation dan connection automation. Setelah otomatisasi selesai, pada blok “axi_timer_0”, klik kanan pada pwm0 -> Make External. Beri nama pin eksternal pwm0 sebagai pwm_Xaxis. Juga, ulangi proses di atas pada blok “axi_timer_1” dan beri nama pin eksternal pwm0 sebagai pwm_Zaxis.

Langkah 6: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (III)

Perhatikan bahwa setiap kali kita menyelesaikan Desain Blok di Vivado, kita perlu membuat Pembungkus HDL. Karena itu akan menjadi modul tingkat atas untuk setiap proyek.

Langkah 7: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (IV)

Sekarang, kita perlu mengatur file kendala kita untuk menetapkan pin yang terhubung ke diagram blok kita. Tutup jendela Desain Blok, Pada tab Sumber, “Tambah Sumber”->Tambahkan atau buat batasan-> tambahkan Zybo-Master.xdc sebagai file batasan kami.

Langkah 8: Membangun Modul PWM- Desain Blok dan Pengaturan File Kendala (V)

Buka file constraint Zybo-Master.xdc dari folder Constraints, batalkan komentar pada port yang ingin kita tentukan sebagai sinyal output dan ganti nama “get_ports{XXXX}”, yang XXXX menunjukkan pin eksternal yang dinamai dalam Diagram Blok. Pengaturan file kendala ditunjukkan pada gambar.

Langkah 9: Membangun Modul PWM- Instalasi Perangkat Keras

Hubungkan motor servo ke Pmod CON3. TowerPro SG90 adalah model motor servo yang kami gunakan dalam proyek ini. Untuk kabel motor servo, kabel oranye mewakili sinyal PWM, terhubung ke pin SIG di Pmod CON3. Kabel merah Vcc adalah kabel listrik yang terhubung ke pin VS di Pmod CON3. Akhirnya, kabel coklat Gnd adalah kabel ground yang terhubung ke pin GND. Selanjutnya, masukkan Pmod CON3 ke baris atas port JD di Zybo Board.

Langkah 10: Membangun Modul PWM- Hasilkan Bitstream dan Luncurkan SDK

1. Di tab Project Navigator, jalankan Generate BitStream.

2. Ekspor perangkat keras: File> Ekspor> Ekspor Perangkat Keras-> tandai pada “sertakan bitstream”-> OK 3. Luncurkan SDK: File -> Luncurkan SDK.

Langkah 11: Membangun Modul PWM- Buat Aplikasi Baru di Xilinx SDK

Buat aplikasi baru:

File > Baru > Proyek Aplikasi -> Masukkan nama proyek Anda -> Selesai

Di bawah Project Explorer, seharusnya ada tiga folder.

Dalam hal ini, “design_1_wrapper_hw_platform_0” adalah folder yang sebelumnya diekspor oleh Vivado. Axis_2_PWM_SDK_bsp adalah folder paket dukungan papan. Dan Axis_2_PWM_SDK adalah folder proyek utama kami di SDK. Anda dapat melihat file "helloworld.c" di bawah folder "src" Axis_2_PWM_SDK, di mana "helloworld.c" adalah file utama.

Langkah 12: Membangun Modul PWM- Gambaran Umum Project Explorer (I)

Mari kita periksa beberapa file di bawah Project Explorer. Pertama, di folder “design_1_wrapper_hw_platform_0”, buka “system.hdf”. File ini menunjukkan peta alamat untuk prosesor ps7_cortex9 dan blok IP yang ada dalam desain kami.

Langkah 13: Membangun Modul PWM- Gambaran Umum Project Explorer (II)

Kemudian, centang file “include” dan “libsrc” di bawah folder “Axis_2_PWM_SDK_bsp”. File library di sini memungkinkan kita untuk berinteraksi dengan periferal perangkat keras tanpa register "bermain".

Langkah 14: Membangun Modul PWM- Tinjauan Proyek Explorer (III)

Melalui dokumentasi BSP, xtmrctr.h ditemukan sebagai Pustaka Kontrol Timer Xilinx yang terkait dengan Timer AXI. Biasanya, kita dapat menemukan fungsi PWM yang diinginkan di sini. Namun, jika Anda membaca dokumentasi “tmrctr_v4_3”, ini menunjukkan bahwa driver saat ini tidak mendukung operasi PWM perangkat. Karena kekurangan fungsi PWM, kami harus menyelesaikan fungsi PWM kami dengan bantuan xtmrctr.h dan AXI Timer v2.0 LogiCORE IP Product Guide.

Langkah 15: Membangun Modul PWM- Membungkus Fungsi PWM (I)

Kembali ke file utama “helloworld.c”, sertakan file header berikut:

Langkah 16: Membangun Modul PWM- Membungkus Fungsi PWM (II)

Tentukan alamat dasar dari dua AXI TImer melalui “xparameters.h”.

Langkah 17: Membangun Modul PWM- Membungkus Fungsi PWM (III)

Bangun fungsi PWM yang diinginkan.

Duty_val: mengubah nilai derajat menjadi duty cycle. PWM_Freq_Duty: mengatur frekuensi dan duty cycle yang diinginkan untuk menghasilkan PWM. Periode jam juga harus ditetapkan.

PWM_START: tetapkan alamat register PWM dan mulai menghasilkan PWM.

PWM_STOP: tetapkan alamat register PWM dan hentikan pembuatan PWM.

Kode demo lainnya ditampilkan di “helloworld.c” di bawah “Axis_2_PWM_SDK”

Langkah 18: Membangun Modul PWM- Jalankan

1. Program FPGA melalui SDK

- Hubungkan Zybo Board melalui port USB ke PC.

- Alat Xilinx -> Program FPGA

2. Jalankan programnya

Klik ikon "Jalankan" dan tarik turun menu -> Jalankan Sebagai -> Luncurkan di Perangkat Keras

3. SDK Terminal

- Buka Terminal SDK -> Hubungkan ke Port Serial -> OK

- Jalankan programnya. Jika kode demo berhasil dijalankan, Anda akan melihat "Inisialisasi selesai!" di Terminal SDK.

Langkah 19: Pemrosesan Video Streaming di Digilent ZYBO Dengan OV7670

File arsip lengkap terlampir.

Langkah 20: Diagram Blok Lengkap

Ini menunjukkan diagram lengkap dari semua koneksi dan blok IP dalam proyek

Langkah 21: Hubungkan OV7670 ke ZYBO

Buat koneksi untuk menyambungkan modul ov7670 ke ZYBO Pmods

Data Pmod adalah Pmod D

Kontrol Pmod adalah Pmod C

Selain itu, sambungkan PmodCON3 dan servos seperti yang ditentukan di paruh pertama tutorial ini

Langkah 22: Buat Desain Blok

Di Flow Navigator, klik "Buat Desain Blok", lalu tekan OK.

Langkah 23: Tambahkan File VHDL untuk Kontrol dan Tangkap Kamera OV7670

Tambahkan file VHDL yang dilampirkan pada langkah ini ke proyek

Langkah 24: Tambahkan File Kendala

Tambahkan file kendala terlampir ke proyek Anda.

Langkah 25: Tambahkan Repo IP untuk HLS IP

Ambil file Zip yang dilampirkan dan unzip ke folder baru bernama sama di direktori (folder) baru bernama "HLS_repo".

Tambahkan repositori IP ke proyek Anda dengan membuka katalog IP dan klik kanan memilih "Tambah Repositori…"

Arahkan ke direktori "HLS_repo" Anda dan pilih.

Opsional: Buat blok pemrosesan video HLS untuk Anda sendiri!

Langkah 26: Tambahkan Modul dan IP

Tambahkan modul ov7670_axi_stream_capture, debounce, dan ov7670_controller ke diagram blok dengan mengklik kanan latar belakang dan memilih "Tambah Modul…"

Demikian pula, tambahkan IP:

- HLS_Video_Track

- Penulisan Penyangga Bingkai Video

- Baca Buffer Bingkai Video

- Pengontrol Waktu Video

- AXI4-Streaming ke Video Out

- 3 dari "Irisan"

- Konstan

- 2 dari AXI Timer

Langkah 27: Pengaturan Konfigurasi IP

Seperti yang ditunjukkan pada gambar

Langkah 28: Tambahkan dan Konfigurasi Blok IP PS

Tambahkan Sistem Pemrosesan ZYNQ7 ke diagram blok

mengedit konfigurasi:

-

Konfigurasi PS-PL

-

HP

- Aktifkan S HP 0

- Aktifkan S HP 1

-

-

Konfigurasi jam

-

Jam Kain PL

- FCLK_0 pada 100MHz

- FCLK_1 pada 25MHz (OutputClock)

- FLCK_2 pada 35MHz (<=50MHz) (Jam Kamera)

-

Langkah 29: Bagian 1. Membangun Modul PWM untuk Motor Servo

Keluarkan axi_timer_0 pwm0 ke port keluaran baru pwm_Xaxis

Keluarkan axi_timer_1 pwm0 ke port keluaran baru pwm_Zaxis

Langkah 30: Koneksi Sisi Input Video (aclk Disorot)

Hubungkan blok IP sisi input video dengan benar

(* koneksi ini harus dibuat dengan memilih opsi yang tepat selama otomatisasi koneksi)"aclk" dari axi_stream_capture pergi ke:

- ap_clk pada penulisan buffer bingkai video

- ap_clk di blok pemrosesan aliran video HLS

- *dapatkan pada IP smartconnect AXI dari Buffer Bingkai Video Tulis ke S_AXI_HP0

- *aclk sesuai dengan saluran IP Interkoneksi AXI untuk saluran S_AXI dari blok pemrosesan video HLS dan buffer bingkai video menulis S_AXI_HP0_ACLK pada blok PS

Sinyal aliran video hanya dihubungkan secara seri dari blok pengambilan ke antarmuka memori Zynq.

- Video beralih dari blok tangkap ke blok pemrosesan HLS.

- Video yang diproses dari blok HLS masuk ke blok tulis frame buffer.

- *Blok tulis penyangga bingkai terhubung ke antarmuka HP0 pada blok Zynq PS.

- Sinyal m_axis_tuser dari output blok penangkapan secara manual disambungkan ke sinyal input video_in_TUSER pada blok pemrosesan HLS dan sinyal ap_start pada blok yang sama.

Sinyal TUSER(tuser) digunakan oleh protokol aliran video AXI untuk menunjukkan awal dari sebuah frame video. AP_Start memberi tahu blok HLS untuk memulai pemrosesan. Oleh karena itu, kami menggunakan tuer untuk memicu blok HLS untuk memproses setiap frame sebagaimana adanya masuk. Saat menghubungkan satu sinyal bus dan memisahkannya dengan cara ini, perlu juga menghubungkannya ke titik terminasi normal dari sisa bus. Vivado mengasumsikan bahwa jika Anda menghubungkan sinyal secara manual, Anda ingin memutuskan apa yang biasanya terhubung.

Pengaturan konfigurasi blok IP:

Buffer bingkai video menulis:

Format video: RGB8

1 sampel per jam Kolom maks: 1280 (>=640) Baris maks: 960 (>=480) Lebar data maks: 8

Langkah 31: Koneksi ke OV7670

Di blok ov7670_axi_stream_capture

- Jadikan semua input eksternal (klik kanan pada pin dan pilih dari menu, atau klik kiri->ctrl+T)

- Biarkan nama apa adanya

Di blok ov7670_controller

- Jadikan semua keluaran blok menjadi eksternal

- Ganti nama port config_finished menjadi led0

- hubungkan clk ke CameraClock (<=50MHz) (FCLK_2)

Di blok debounce

- sambungkan input button1 ke port input eksternal yang disebut btn0

- hubungkan out1 ke jalur kirim ulang pada blok IP ov7670_controller

- sambungkan input button2 ke port input eksternal yang disebut btn3

- hubungkan out2n ke input ext_reset_in pada IP Reset Sistem Prosesor untuk domain jam pengambilan video. (*Ini mungkin perlu dilakukan setelah IP dibuat*)

- sambungkan clk ke CameraClock (<=50MHz) (FCLK_2)

Langkah 32: Koneksi di Sisi Luar Video

Koneksi untuk blok Video Timing Controller (VTC), AXI4-Stream ke Video Out, dan irisan

- Gunakan jam 25MHz (FCLK_1) untuk vid_io_out_clk dan VTC clk

- Gunakan jam 100MHz (FCLK_0) untuk aclk di AXI4-Stream to Video Out

- vtiming_out ke vtiming_in

- Video Frame Buffer Baca m_axis_video masuk ke AXI4-Stream ke Video Out video_in

- vtg_ce pergi ke gen_clken

- Ikat clken VTC, aclken, vid_io_out_ce ke Constant dout[0:0]

- Bawa vid_hsync dan vid_vsync masing-masing ke port output eksternal vga_hs dan vga_vs. (tidak difoto)

Irisan:

-

Irisan harus diatur seperti yang ditunjukkan pada gambar terlampir

- ganti nama blok menjadi slice_red, slice_green, dan slice_blue

- atur rentang irisan seperti yang ditunjukkan pada gambar per nama blok

- hubungkan setiap keluaran irisan ke keluaran port eksternal seperti yang ditunjukkan pada gambar.

- vid_data[23:0] terhubung ke input untuk setiap irisan (Din[23:0])

Langkah 33: Jalankan Blokir dan Otomatisasi Koneksi

Jalankan Block Automation untuk menghubungkan hal-hal dari blok ZYNQ7 PS. Seperti yang ditunjukkan oleh gambar.

Jalankan otomatisasi Koneksi untuk membuat semua IP interkoneksi. Perhatikan baik-baik semua opsi di setiap gambar.

Pada blok debounce, sambungkan out2n ke domain jam pengambilan video. Prosesor Sistem Reset input ext_reset_in.

Langkah 34: Hasilkan Pembungkus HDL

Hasilkan Pembungkus HDL untuk desain blok Anda.

Tetapkan sebagai modul teratas.

Langkah 35: Hasilkan Bitstream, Ekspor Perangkat Keras ke SDK, Luncurkan SDK Dari Vivado

Pastikan untuk menyertakan bitstream dalam ekspor.

Generasi bitstream mungkin memakan waktu yang sangat lama.

Kemudian luncurkan SDK

Langkah 36: SDK (tanpa FreeRTOS)

Versi ini melakukan segalanya tanpa menggunakan FreeRTOS, memadatkan kode dengan baik.

Buat BSP mandiri berdasarkan desain perangkat keras. Opsi default harus baik-baik saja. Pastikan sumber BSP telah dibuat.

Buat Aplikasi seperti yang ditunjukkan pada Gambar. (aplikasi kosong)

Hapus file utama yang dibuat secara otomatis dan impor file terlampir.

Langkah 37: Implementasi FreeRTOS

Versi ini memang menggunakan FreeRTOS. Buat BSP FreeRTOS901 berdasarkan desain perangkat kerasnya. Opsi default harus baik-baik saja. Pastikan sumber BSP telah dibuat.

Buat Aplikasi seperti yang ditunjukkan pada Gambar. (aplikasi kosong)

Hapus file utama yang dibuat secara otomatis dan impor file terlampir.

Langkah 38: Petunjuk Penggunaan

Proyek ini agak sulit untuk dijalankan. Ikuti langkah-langkahnya secara berurutan.

Pastikan ZYBO Anda tidak memuat sendiri apa pun saat dihidupkan. Ini berarti LED Selesai seharusnya tidak menyala. Salah satu cara untuk melakukannya adalah dengan menyetel jumper sumber boot ke JTAG.

Buka proyek (FreeRTOS atau tidak) yang ingin Anda program dari SDK

- Nyalakan ZYBO Anda. LED Selesai seharusnya tidak menyala.

- Program FPGA dengan file bit. LED Selesai akan menyala. Led0 seharusnya tidak menyala.

- Jalankan kode (ingat untuk melewati breakpoint awal jika Anda melakukannya).

Pada titik ini Anda harus mendapatkan output pada layar VGA Anda.

Untuk memulai ulang (jika bug atau apa pun): ketuk tombol PS-SRST dengan cepat atau matikan ZYBO lalu nyalakan kembali. Lanjutkan dari langkah 2.

Menghentikan prosesor dengan debugger akan menyebabkan Kamera menahan posisi alih-alih bergerak. Streaming video akan tetap berlanjut.

Langkah 39: Referensi dan Tautan

Panduan referensi dan dokumentasi Xilinx:

- PG044 - AXI-Stream ke Video Out

- PG278 - Buffer Bingkai Video Baca/Tulis

Tautan lainnya:

- blog Lauri - masukan VDMA

- Blog Lauri - Output OV7670 ke VGA menggunakan BRAM

- Wiki Hamsterworks, oleh Mike Fields, sumber asli kode OV7670

- Lembar data yang menunjukkan spesifikasi waktu dasar

Direkomendasikan:

Kontrol Gerakan Sederhana - Kontrol Mainan RC Anda Dengan Gerakan Lengan Anda: 4 Langkah (dengan Gambar)

Kontrol Gerakan Sederhana - Kontrol Mainan RC Anda Dengan Gerakan Lengan Anda: Selamat datang di 'ible' saya #45. Beberapa waktu yang lalu saya membuat BB8 versi RC yang berfungsi penuh menggunakan bagian Lego Star Wars … https://www.instructables.com/id/Whats-Inside-My-R…Ketika saya melihat betapa kerennya itu Force Band yang dibuat oleh Sphero, saya berpikir: "Ok, saya c

Pan Tilt Dikendalikan oleh Ponsel: 4 Langkah

Pan Tilt Dikendalikan oleh Ponsel: Halo semua, Dalam proyek baru saya ini, saya akan memperkenalkan kepada Anda Pan-Tilt yang dikendalikan oleh Ponsel. Semua gerakan ponsel direproduksi dalam perangkat pan-tilt melalui Bluetooth. Konstruksinya sangat sederhana menggunakan Arduino R3 (atau serupa) dan dua

Mekanisme Pan dan Tilt untuk Time Lapse DSLR: 7 Langkah (dengan Gambar)

Mekanisme Pan dan Tilt untuk Time Lapses DSLR: Saya memiliki beberapa motor stepper yang tergeletak di sekitar dan benar-benar ingin menggunakannya untuk membuat sesuatu yang keren. Saya memutuskan bahwa saya akan membuat sistem Pan and Tilt untuk kamera DSLR saya sehingga saya dapat membuat selang waktu yang keren. Item yang Anda perlukan: 2x motor stepper -htt

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: 9 Langkah (dengan Gambar)

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: Sebagian besar desain DIY untuk pelacak surya sumbu ganda "di luar sana" didasarkan pada Servo Mikro 9G yang benar-benar di bawah nilai untuk mendorong beberapa Sel Surya, pengontrol mikro, baterai, dan rumahan. Anda dapat mendesain sekitar

Kontrol Multi Servo Pan-Tilt: 11 Langkah (dengan Gambar)

Kontrol Multi Servo Pan-Tilt: Pada tutorial ini, kita akan mengeksplorasi cara mengontrol beberapa servo menggunakan Python pada Raspberry Pi. Tujuan kami adalah mekanisme PAN/TILT untuk memposisikan kamera (PiCam). Di sini Anda dapat melihat bagaimana proyek akhir kami akan bekerja: Control Servo Control loop test: