Daftar Isi:

- Pengarang John Day [email protected].

- Public 2024-01-30 09:54.

- Terakhir diubah 2025-01-23 14:49.

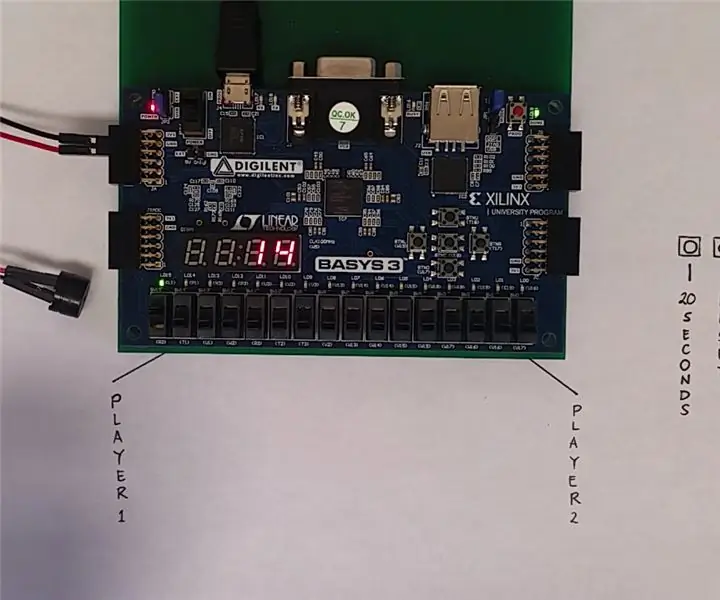

Sistem buzzer kompetitif yang dirancang dalam proyek ini beroperasi serupa dengan sistem buzzer yang digunakan dalam Kompetisi Science Bowl Regional dan Nasional. Proyek ini terinspirasi oleh keterlibatan saya dengan tim mangkuk sains sekolah menengah saya selama tiga tahun. Kami selalu memiliki keinginan untuk membuat ulang sistem buzzer lock-out dengan timer 5 detik dan 20 detik.

Untuk memberikan beberapa latar belakang pada sistem buzzer, buzzer mangkuk sains diprogram untuk memasukkan maksimal 8 pemain (dengan 8 buzzer terpisah). Setelah satu buzzer ditekan, buzzer orang pertama akan menyala untuk menunjukkan pemain mana yang menerima pertanyaan. Pemain lainnya akan "dikunci" yang berarti buzzer mereka tidak akan merespon sampai moderator mengatur ulang sistem buzzer.

Setelah moderator membaca pertanyaan, dia akan menekan tombol untuk memulai penghitung waktu mundur yang akan ditampilkan pada tampilan tujuh segmen. Setelah pertanyaan "toss-up", moderator dapat menekan tombol kanan untuk memulai hitungan mundur dari 5 detik. Sementara itu, setelah pertanyaan "bonus", moderator dapat menekan tombol kiri untuk memulai hitungan mundur dari 20 detik. Setelah penghitung waktu mencapai nol, bel suara akan menunjukkan bahwa pemain telah kehabisan waktu.

Untuk mengatur ulang sistem dan penghitung waktu mundur, moderator dapat menekan tombol tengah. Untuk mengatur ulang mekanisme penguncian dan LED pemutar, sakelar untuk pemutar 1 dan pemutar 2 harus dalam posisi rendah.

Langkah 1: Bahan

Anda akan membutuhkan yang berikut ini:

- Papan Basys3 (atau papan FPGA yang setara)

- Kabel USB Mikro-B

- Speaker (saya menggunakan speaker pasif)

- 2 kabel

- Perangkat lunak untuk diterapkan pada FPGA (saya menggunakan Vivado)

- File Sistem Buzzer Kompetitif

Langkah 2: Diagram Kotak Hitam

Diagram kotak hitam menunjukkan input dan output yang akan digunakan pada sistem buzzer ini.

MASUKAN:

player1, player2 Input ini terhubung ke dua sakelar di papan Basys3. Untuk kenyamanan, sakelar paling kiri dan paling kanan akan digunakan.

reset Tombol tengah akan digunakan untuk mewakili tombol reset.

count_down_20_sec Tombol kiri akan digunakan untuk mewakili tombol pengatur waktu 20 detik.

count_down_5_sec Tombol kanan akan digunakan untuk mewakili tombol pengatur waktu 20 detik. Untuk memastikan timer 20 detik dan 5 detik dimulai, tahan tombol hingga tampilan tujuh segmen menampilkan timer.

CLK Papan FPGA akan menghasilkan jam yang berjalan dengan frekuensi 10 ns.

KELUARAN:

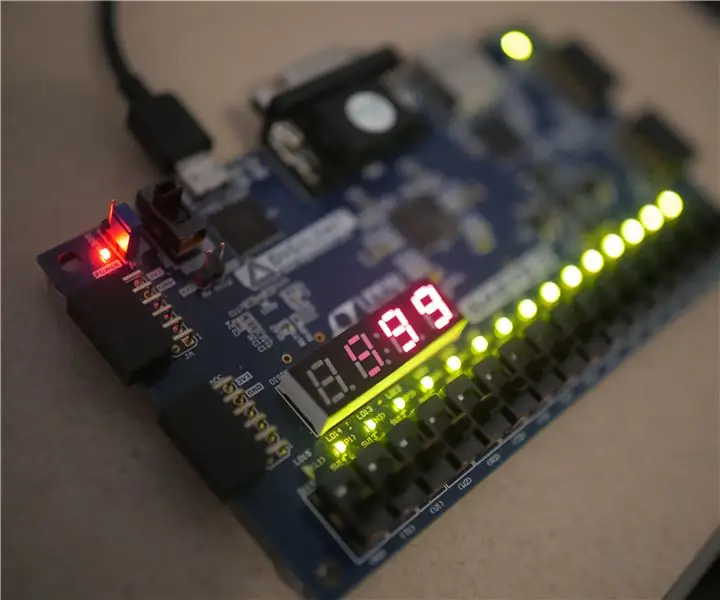

speaker Output speaker terhubung ke buzzer atau speaker eksternal. Anda harus menghubungkan speaker ke port pmod JA papan Basys3. Langkah ini akan diuraikan di bawah ini.

speaker_LED Output ini terhubung ke LED di tengah papan, dan hanya akan menunjukkan ketika output speaker FPGA tinggi. Anda dapat menggunakan ini untuk menguji speaker eksternal Anda. Perhatikan bahwa beberapa port pmod mungkin tidak berfungsi dengan baik, jadi Anda dapat mencoba yang berbeda dan menggunakan LED untuk memeriksa apakah speaker harus menyala.

SEGMEN Output ini terhubung ke delapan segmen individu pada tampilan tujuh segmen, termasuk titik desimal.

DISP_EN Output ini terhubung ke empat anoda pada tampilan tujuh segmen.

player_LED Output ini adalah sinyal 2-bundel yang terhubung ke LED di atas sakelar pemutar1 dan pemutar2. Pemain pertama yang membalik sakelar yang sesuai akan ditunjukkan oleh LED. Perhatikan bahwa kedua LED tidak dapat menyala secara bersamaan.

Langkah 3: Menghubungkan Speaker Eksternal

Untuk menghubungkan speaker eksternal ke papan Basys3, ambil dua kabel Anda dan pasang seperti yang ditunjukkan pada gambar di atas. Garis putih menghubungkan terminal negatif speaker ke port ground pada board. Garis merah menghubungkan terminal positif speaker ke port pmod JA10 di papan.

File kendala dirancang agar port apa pun dari JA1 hingga JA10 dapat berfungsi. Namun, beberapa pin di papan tidak responsif, jadi jika JA10 tidak berfungsi, Anda dapat mencoba port lain.

Langkah 4: Diagram Struktural

Gambar di atas menunjukkan diagram struktur sistem buzzer kompetitif termasuk semua komponen yang membentuk modul utama. Deskripsi mereka adalah sebagai berikut:

player_lockout_LED1 Komponen LED penguncian pemutar adalah mesin keadaan terbatas yang menggunakan penyandian satu-panas. Ini memiliki empat input: player1, player2, reset, dan CLK. Ini berisi output bundel 2-bit player_LED. Input dan output dari komponen player_lockout_LED1 semuanya terhubung langsung ke input dan output modul utama dengan nama yang sama.

buzzer_tone1 Komponen buzzer didasarkan pada kode ini yang diposting di forum

stackoverflow.com/questions/22767256/vhdl-… Namun, itu dimodifikasi untuk mengeluarkan suara kontinu dengan frekuensi 440 Hz (Catatan). Input enable terhubung ke sinyal buzzer_enable yang merupakan output dari komponen down_counter_FSM1.

clk_div1 Komponen pembagi jam adalah versi modifikasi dari pembagi jam Profesor Bryan Mealy yang disediakan di PolyLearn. Ini memperlambat jam sehingga periode output adalah 1 detik.

down_counter_FSM1 Penghitung turun adalah FSM yang dirancang untuk menghitung mundur hingga nol. Dua kemungkinan waktu mulai adalah 20 atau 5 yang dipilih oleh input pengguna. Ini output '1' ketika timer telah mencapai nol untuk menunjukkan bahwa waktu telah habis. Output ini bertindak sebagai enable untuk komponen nada buzzer. Penghitung juga mengeluarkan sinyal bundel 8-bit yang mengirimkan BCD 8-bit yang dikirim ke dekoder segmen. Output lainnya adalah counter_on yang juga terhubung ke input valid pada decoder segmen.

sseg_dec1 Komponen dekoder tujuh segmen disediakan di PolyLearn dan ditulis oleh Profesor Bryan Mealy. Ini menggunakan input BCD yang disediakan oleh down_counter_FSM1, dan mengeluarkan ekuivalen desimal pada tampilan tujuh segmen. Ketika penghitung menyala, maka input yang valid adalah tinggi. Ini memungkinkan dekoder untuk menampilkan angka desimal pada tampilan tujuh segmen. Ketika penghitung mati, maka input yang valid adalah rendah. Tampilan tujuh segmen kemudian hanya akan menampilkan empat tanda hubung.

Langkah 5: Diagram Finite State Machine (FSM)

Daftar sensitivitas untuk mesin keadaan terbatas termasuk player1, player2, reset, dan jam. Output FSM adalah bundel 2-bit player_LED yang terhubung ke dua LED pada papan Basys3. Mesin Keadaan Hingga menunjukkan tiga keadaan berikut:

ST0 adalah keadaan awal. Dalam keadaan ini, kedua LED dimatikan. FSM akan tetap dalam status ini jika player1 dan player2 rendah. Reset asinkron juga menetapkan status ke ST0. Saat sakelar pemutar1 disetel ke tinggi, status berikutnya adalah ST1. Jika sakelar player2 disetel ke tinggi, status berikutnya adalah ST2.

ST1 adalah status LED player1 menyala. FSM akan tetap dalam status ini untuk input apa pun. Ini berarti bahwa meskipun sakelar pemutar2 disetel ke tinggi segera setelah sakelar pemutar1 tinggi, sakelar itu akan tetap berada di ST1. Hanya reset asinkron yang dapat mengatur status berikutnya ke ST0.

ST2 adalah status LED player2 menyala. Mirip dengan ST!, FSM akan tetap dalam status ini untuk input apa pun, bahkan ketika sakelar pemutar1 disetel ke tinggi segera setelah sakelar pemutar2 tinggi. Sekali lagi, hanya reset asinkron yang dapat mengatur status berikutnya ke ST0.

Direkomendasikan:

Piano Buzzer Arduino Piezo: 5 Langkah

Arduino Piezo Buzzer Piano : Disini kita akan membuat piano Arduino yang menggunakan buzzer piezo sebagai speakernya. Proyek ini mudah diskalakan dan dapat bekerja dengan lebih banyak atau lebih sedikit catatan, tergantung pada Anda! Kami akan membangunnya hanya dengan empat tombol/kunci untuk kesederhanaan. Ini adalah proyek yang menyenangkan dan mudah

CARA MENGANTARMUKA BUZZER PASIF DENGAN ARDUINO: 4 Langkah

CARA MENGANTARMUKA BUZZER PASIF DENGAN ARDUINO: Membuat suara pada arduino adalah proyek yang menarik, hal ini dapat diselesaikan dengan menggunakan modul dan perangkat yang berbeda tergantung pada proyek dan pilihan Anda. Dalam proyek ini, kita akan melihat cara Anda dapat membuat suara dengan bel. Buzzer yang digunakan oleh

Sistem Penyortiran Warna: Sistem Berbasis Arduino Dengan Dua Sabuk: 8 Langkah

Sistem Penyortiran Warna: Sistem Berbasis Arduino Dengan Dua Sabuk: Pengangkutan dan/atau pengemasan produk dan barang di bidang industri dilakukan dengan menggunakan jalur yang dibuat menggunakan ban berjalan. Sabuk tersebut membantu memindahkan barang dari satu titik ke titik lain dengan kecepatan tertentu. Beberapa tugas pemrosesan atau identifikasi mungkin

Game Waktu Kompetitif 2 Pemain VS: 4 Langkah

2 Pemain Kompetitif VS Timing Game: Anda akan membutuhkan:1.Digilent Basys 3, FPGA Board (atau FPGA lainnya,)2. Versi Vivado yang relatif terbaru, atau lingkungan VHDL lainnya3. Komputer yang dapat menjalankan program tersebut

Cara Benar Menghubungkan dan Mengatur Sistem Rak Mini HiFi (Sistem Suara): 8 Langkah (dengan Gambar)

Cara Menghubungkan dan Mengatur Sistem Rak Mini HiFi (Sound System) dengan Benar: Saya adalah orang yang senang belajar tentang teknik elektro. Saya seorang sekolah menengah di Sekolah Ann Richards untuk Pemimpin Remaja Putri. Saya membuat instruksi ini untuk membantu siapa saja yang ingin menikmati musik mereka dari Mini LG HiFi Shelf Syste