Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:55.

- Terakhir diubah 2025-06-01 06:09.

Saya kewalahan oleh jenis tanggapan yang saya dapatkan di blog ini. Terima kasih teman-teman telah mengunjungi blog saya dan memotivasi saya untuk berbagi pengetahuan dengan Anda. Kali ini, saya akan menyajikan desain modul menarik lainnya yang kita lihat di semua SOC -- Interrupt Controller.

Kami akan merancang Programmable Interrupt Controller yang sederhana namun kuat. Ini adalah desain yang sepenuhnya dapat dikonfigurasi dan diparameterisasi yang portabel di seluruh platform. Saya merancang ini setelah membaca banyak tentang beberapa arsitektur pengontrol interupsi populer di luar sana seperti NVIC, 8259a, RISC-V PLIC, INTC Microblaze, dll. Semoga blog ini bermanfaat bagi Anda dan membantu Anda memahami bagaimana interupsi ditangani oleh prosesor dengan bantuan Interrupt Controller.

Langkah 1: Spesifikasi

Berikut adalah spesifikasi dari IP:

- Antarmuka AHB3-Lite.

-

Parameter yang dapat dikonfigurasi secara statis:

- Jumlah sumber interupsi eksternal; mendukung hingga 63 interupsi.

- Jumlah tingkat prioritas; mendukung hingga 63 level.

- Jumlah tingkat bersarang; mendukung hingga 8 tingkat bersarang.

- lebar bus; 32 atau 64.

- Interupsi yang dapat disembunyikan secara global dan lokal.

- Tingkat prioritas yang dapat dikonfigurasi secara dinamis untuk setiap interupsi.

- Dua mode operasi - Fully Nested Mode dan Equal Priority Mode.

- Mendukung interupsi sensitif tingkat tinggi aktif.

Spesifikasi RISC-V PLIC terinspirasi mekanisme interupsi handshaking digunakan dalam desain.

Pre-emption interupsi terinspirasi dari 8259a

Bacaan lainnya: Microblaze INTC, NVIC

Langkah 2: Ikhtisar PIC

Programmable Interrupt Controller (PIC) menerima beberapa interupsi dari periferal eksternal dan menggabungkannya menjadi satu output interupsi ke inti prosesor target.

PIC dikendalikan melalui kontrol dan register status. Semua register PIC dipetakan memori, dan diakses melalui antarmuka bus AHB3-Lite.

Bank register terdiri dari register konfigurasi, register aktif, register tertunda, register in-service, register prioritas, dan register ID, yang merupakan tipikal dalam Interrupt Controller.

Register konfigurasi digunakan untuk mengatur mode operasi PIC. Ini dapat bekerja dalam Mode Bersarang Penuh atau Mode Prioritas Sama.

Setiap interupsi dapat diberikan prioritas dan ditutup secara individual. Masking global dari semua interupsi juga didukung.

Bank register berinteraksi dengan Priority Resolver dan BTC (Binary-Tree-Comparator) untuk menyelesaikan prioritas interupsi yang tertunda dan menegaskan interupsi ke prosesor yang sesuai. Register ID berisi ID dari interupsi tertunda dengan prioritas tertinggi.

Langkah 3: Desain dan Implementasi RTL

Desain PIC menekankan pada pengurangan latensi penyelesaian prioritas, yang merupakan bagian paling kritis dari desain. Karena desain menyelesaikan prioritas dalam satu siklus clock, kinerja menurun seiring dengan peningkatan jumlah sumber dengan kompleksitas Log2.

Desain berhasil diimplementasikan dan waktu diverifikasi hingga frekuensi berikut pada FPGA Artix-7.

- Hingga 15 sumber: 100 MHz

- Hingga 63 sumber: 50 MHz

Interrupt Latency yang ditambahkan oleh PIC saja adalah 3 siklus clock (Tidak termasuk waktu sakelar konteks Prosesor dan waktu pengambilan instruksi ISR pertama).

Langkah 4: Catatan Penting dan File Terlampir

Catatan penting:

- Jika antarmuka AHB3-Lite tidak diinginkan, Anda dapat mengubah modul atas dan menggunakan desain kerangka PIC. Namun bangku tes yang disediakan adalah untuk IP dengan Antarmuka AHB3-Lite.

- PIC IP v1.0 adalah desain RTL yang benar-benar portabel.

- Secara fungsional diverifikasi untuk bekerja pada kedua mode.

File-file terlampir:

- Kode desain dan testbench di VHDL.

- Dokumentasi IP Lengkap.

Ini adalah desain open-source … Jangan ragu untuk menggunakan …

Untuk pertanyaan apa pun, kapan pun:

Mitu Raj

Direkomendasikan:

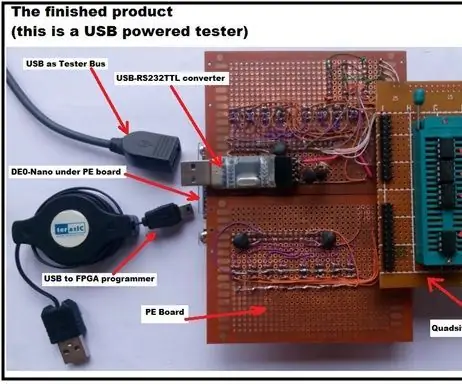

Renegade-i (Penguji IC yang Dapat Diprogram yang Terasa Seperti Nyata): 3 Langkah (dengan Gambar)

Renegade-i (Penguji IC yang Dapat Diprogram yang Terasa Seperti Nyata): MIMPI JUTA DOLLAR. Pernahkah Anda bermimpi memiliki penguji IC sendiri di rumah? Bukan sekedar gadget yang bisa menguji IC, tapi mesin “programmable” yang terasa seperti salah satu produk unggulan dari pemain terbesar di industri pengujian semicon

Desain Pengontrol Cache Sederhana di VHDL: 4 Langkah

Desain Pengontrol Cache Sederhana di VHDL: Saya menulis instruksi ini, karena saya merasa agak sulit untuk mendapatkan beberapa kode referensi VHDL untuk belajar dan mulai merancang pengontrol cache. Jadi saya merancang pengontrol cache sendiri dari awal, dan mengujinya dengan sukses di FPGA. saya punya p

Seni 2D Dengan LED yang Dapat Diprogram dan Basis dan Logo yang Dapat Disesuaikan: 5 Langkah (dengan Gambar)

Seni 2D Dengan LED yang Dapat Diprogram dan Basis dan Logo yang Dapat Disesuaikan: Selamat datang di instruksi! Hari ini, saya akan menunjukkan cara membuat Proyek Seni 2D dengan logo dan desain keseluruhan pilihan Anda. Saya membuat proyek ini karena dapat mengajarkan orang banyak keterampilan seperti pemrograman, pengkabelan, pemodelan 3D, dan lainnya. Ini

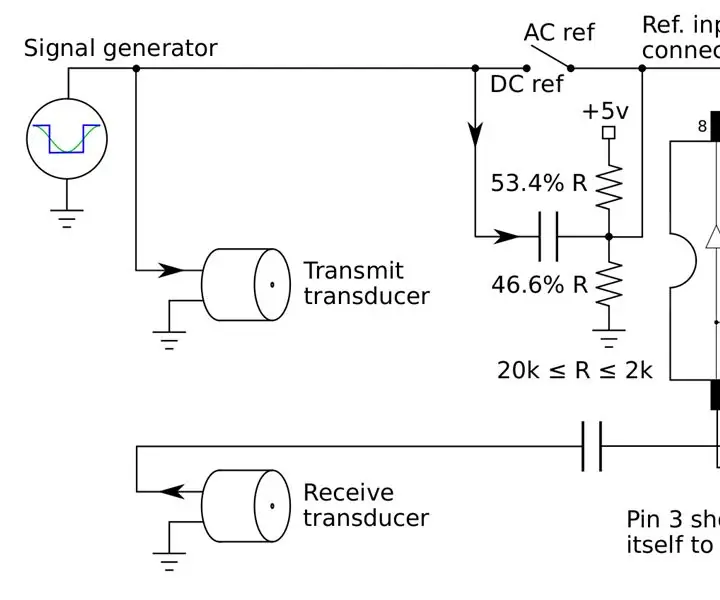

Penguat Pengunci Miniatur yang Dapat Dipakai (dan Sistem Sonar untuk Perangkat yang Dapat Dipakai, Dll.): 7 Langkah

Penguat Penguncian Miniatur yang Dapat Dipakai (dan Sistem Sonar untuk Perangkat yang Dapat Dikenakan, Dll.): Bangun penguat pengunci mini murah yang dapat disematkan dalam bingkai kacamata dan untuk membuat sistem penglihatan sonar untuk orang buta, atau ultrasound sederhana mesin yang terus memantau jantung Anda dan menggunakan Pembelajaran Mesin Manusia untuk memperingatkan p

Pengumpan Ikan Akuarium yang Dapat Diprogram - Makanan Granulasi yang Dirancang: 7 Langkah (dengan Gambar)

Pengumpan Ikan Akuarium yang Dapat Diprogram - Makanan Granulasi yang Dirancang: Pengumpan ikan - makanan butiran yang dirancang untuk ikan akuarium. Desain pengumpan ikan otomatis yang sangat sederhana. Dioperasikan dengan micro servo 9g SG90 kecil dan Arduino Nano. Anda memberi daya seluruh pengumpan dengan kabel USB (dari pengisi daya USB atau port USB