Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:53.

- Terakhir diubah 2025-01-23 14:49.

JDM adalah pemrogram PIC yang populer karena menggunakan port serial, komponen minimal dan tidak memerlukan catu daya. Tapi ada kebingungan di luar sana, dengan banyak variasi programmer di internet, mana yang bekerja dengan PIC yang mana? Dalam "instruksi" ini kami menguji JDM dan saya mendemonstrasikan cara mensimulasikan rangkaian menggunakan Spice yang akan menjawab semua pertanyaan Anda!

Perlengkapan

LTspice yang dapat diunduh dari Perangkat Analog di sini.

Anda juga memerlukan file sirkuit JDM di sini.

Langkah 1: Persyaratan Port Serial

JDM memerlukan port serial yang memenuhi spesifikasi EIA232, idealnya dengan level tegangan +12/-12.

Menurut lembar data Texas Instruments Line Driver MC1488 (Gambar 3)

Impedansi keluaran = 4V/8mA = 500 ohm.

Batas arus hubung singkat = 12mV, tanpa batas waktu - tidak ada kerusakan pada chip.

Impedansi masukan penerima saluran = 3k hingga 7k ohm direkomendasikan.

Port serial pada PC desktop lama menggunakan +12v/-12V yang memenuhi persyaratan ini.

Port serial pada PC laptop yang lebih baru menggunakan voltase yang lebih rendah. JDM mungkin atau mungkin tidak bekerja - jawabannya lebih kompleks.

Langkah 2: Persyaratan Pemrograman PIC

Informasi mengenai persyaratan pemrograman PIC diperoleh dari Microchip. Di atas adalah untuk perangkat biasa.

Langkah 3: Spesifikasi JDM

Apakah situs web JDM asli telah hilang dalam kabut waktu? Ini membuat kita menebak-nebak apa yang awalnya dimaksudkan oleh perancang untuk spesifikasinya.

- Sediakan VDD=5V, dan maksimum IDD=2mA (untuk versi “in socket”)

- Berikan VHH=13V, dan maksimum hingga IHH=0.2mA.

- MCLR Waktu naik tVHHR = 1uS maks.

- Versi ICSP harus mampu menarik MCLR rendah terhadap 22k pull-up tepat sasaran.

Langkah 4: Deskripsi Sirkuit

Gambar JDM1 didasarkan pada rangkaian JDM "standar" yang diambil dari situs web PICPgm. Ini adalah programmer "PIC in Socket" di mana PIC mengambil daya dari pin TX dan RTS. Diagram aslinya sulit dimengerti, jadi saya menggambar ulang menggunakan konvensi normal aliran arus dari atas ke bawah. Dan saya telah menambahkan indikator LED "RESET", "PROG" dan "RTS" yang diperlukan selama konstruksi dan pengujian. Semoga ini tidak berdampak buruk pada perilaku.

Konvensi normal desain sirkuit adalah untuk semua ground, tetapi fitur utama JDM adalah bahwa ground serial port (GND) terhubung ke VDD. Ini menciptakan kebingungan karena sinyal port serial diukur sehubungan dengan GND, sinyal PIC sehubungan dengan ground logika (VSS).

Ketika TX menjadi tinggi, Q1 berperilaku sebagai dua dioda bias maju. (Kolektor Q1 tidak bias mundur seperti pada operasi transistor normal). Kolektor Q1 mengisi C2, yang dijepit pada VDD+8V oleh Zener (D3). emitor Q1 memberikan 13V ke MCLR untuk Program/Verifikasi Mode.

Ketika TX menjadi rendah, kapasitor C3 diisi melalui D1 dan VSS dijepit pada VDD-5V oleh zener (D5). Juga TX dijepit di (VSS-0.6) oleh D1. Q1 mati, C1 menahan muatannya untuk pulsa pemrograman berikutnya. MCLR dijepit pada 0V oleh D2, sehingga PIC sekarang Reset.

Ketika RTS tinggi, clock ditransmisikan ke PGC. D4 menjepit PGC pada logika VDD tinggi. Ketika RTS rendah, kapasitor C3 diisi melalui D6 dan VSS dijepit pada VDD-5V oleh zener (D5). D6 menjepit PGC pada VSS atau logika 0.

Selama pemrograman, data yang dikirim pada DTR dibaca pada PGD, yang dikonfigurasi oleh PIC sebagai input. Ketika DTR tinggi, Q2 bertindak sebagai "pengikut emitor" dan tegangan PGD sekitar (VDD-0,6) atau logika 1. Ketika DTR rendah, Q2 bertindak sebagai transistor buruk (pin emitor dan kolektor terbalik). Q2 menarik PGD rendah, yang dijepit oleh D7 pada VSS atau logika 0.

Selama verifikasi, PIC mengkonfigurasi PGD sebagai output untuk mengirim data ke port serial. DTR harus disetel tinggi, dan data dibaca di CTS. Ketika output PGD tinggi, Q2 mati, CTS = DTR = +12V. Ketika output PGD rendah, Q2 aktif. Kolektor Q2 menarik arus (12V+5V)/(1k+1k5)=7mA dari DTR, dan menarik CTS rendah, ke VSS.

Langkah 5: Bersiaplah untuk Simulasi

Unduh LT spice, simpan dan buka file sirkuit (*.asc) yang disediakan di sini. Untuk mensimulasikan rangkaian, kita harus memberinya beberapa input, lalu "menelusuri" outputnya. V1, V2 V3 mensimulasikan port serial 12V dengan impedansi keluaran R11, R12, R13.

- V1 menghasilkan 2 Pulsa Program pada TX dari 0,5 md hingga 4,5 md

- V2 menghasilkan ledakan pulsa data pada DTR dari 1,5 hingga 4,5 ms

- V3 menghasilkan ledakan pulsa clock pada RTS dari 0,5 hingga 3,5 ms

Komponen V4, X1, R15 dan R16 semuanya merupakan bagian dari simulasi.

- V4 menghasilkan 2 pulsa dari 2,5 hingga 4,5 ms untuk memverifikasi data.

- Jumper X1 mensimulasikan OUTPUT pada PGD.

- R15, R16 mensimulasikan "pemuatan" PIC pada VDD dan MCLR.

Langkah 6: Modifikasi untuk ICSP

Gambar JDM3 menunjukkan versi untuk pemrograman "dalam sirkuit". Modifikasi dari aslinya adalah

- Ganti soket ZIF dengan konektor ICSP.

- PIC sekarang didukung oleh suplai ke sirkuit target (V5).

- Lepaskan zener 5V (D5).

- Kapasitor 100pF kecil (C4) dipindahkan di sebelah PIC pada rangkaian target.

- LED mengambil daya dari papan sirkuit jika memungkinkan.

- Resistor pull-up MCLR (R10) dan dioda (D10) diperlukan pada rangkaian target.

- PERINGATAN. Papan target harus memiliki pasokan "mengambang", idealnya baterai.

- Jangan menghubungkan ground target (VSS) ke ground komputer/PC dengan menghubungkan port komputer lain pada saat yang sama dengan JDM.

Setelah simulasi JDM1, masalah waktu pengisian yang lama pada C2 menjadi jelas. Kemudian setelah membaca Fruttenboel ternyata ditambahkan C2 dan Q1 sebagai modifikasi dari aslinya. Saya tidak bisa memikirkan apa yang dimaksudkan untuk dilakukan C2 dan Q1 selain menciptakan masalah. Jadi untuk JDM4, kami kembali ke desain lama di Fruttenboel yang sederhana dan mudah dipahami. D1 dan D3/LED2 menjepit MCLR antara VSS dan VDD+8V. Nilai R1 dikurangi menjadi 3k3, cukup untuk menerangi LED2 pada 12V.

JDM4 juga dirancang untuk bekerja dengan port serial yang lebih lemah. Ketika TX menjadi tinggi (+9V), sumber arus TX = (9-8)/(1k +3k3) = 0,2ma, cukup untuk menarik MCLR tinggi meskipun tidak cukup untuk menerangi LED2. Ketika TX menjadi rendah (sekitar -7V), arus TX tenggelam =(9-7)/1k = 2mA. LED1 saat ini = (7-2 untuk led)/(2k7) = 1.8mA. Arus tarik MCLR = 7-5.5/3k3 = 0.5mA.

Sirkuit ini juga telah diuji (simulasi JDM5) untuk melihat apa yang terjadi dengan port serial minimum +/-7V, di mana tegangan tidak cukup untuk mempertahankan VHH=13V. Tujuan C1 sekarang menjadi jelas, C1 menciptakan dorongan +ve pendek ke MCLR, lonjakan 33us di tepi naik TX, cukup lama untuk PIC masuk ke mode pemrograman, mungkin? Tetapi lepaskan jumper X2 (nonaktifkan LED1) karena arus tidak cukup untuk menarik MCLR rendah dan menerangi LED1 bersama-sama. Ketika TX menjadi rendah, arus TX tenggelam = (7V-5.5V)/(1k+3k3) = 0.3mA, cukup untuk menarik MCLR rendah terhadap pull-up R10.

Langkah 7: Hasil Simulasi

Untuk melihat file grafik, lebih baik klik kanan tautan di bawah, lalu pilih "Buka tautan di Tab Baru"

Simulasi 1: jejak MCLR, VSS, dan RTS untuk JDM1 asli. Pengamatan 1, 2 dan 3 segera terlihat.

Simulasi 2: jejak MCLR dan VSS, dan RTS untuk JDM2 yang dimodifikasi, yang memperbaiki masalah sebelumnya.

Simulasi 3: jejak PGD, VSS dan PGC untuk JDM2 mengirim data dalam mode program. Pengamatan 4 pada 3.5mS.

Simulasi 4: jejak PGD, VSS dan CTS untuk JDM2 dalam mode verifikasi (jumper X1 dimasukkan). oke

Simulasi 5: jejak MCLR, VSS, PGD dan PGC untuk JDM3. ICSP menggunakan daya dari rangkaian memecahkan banyak masalah.

Simulasi 6: jejak MCLR, VSS, PGD dan PGC untuk JDM4 dengan port serial +/-9V. MCLR segera naik, berfungsi penuh.

Simulasi 7: jejak MCLR, VSS, dan TX untuk JDM5 dengan port serial +/-7V dan jumper X2 dihilangkan. C1 menciptakan dorongan +ve (spike) pada tepi naik MCLR, hampir cukup untuk mendorong MCLR di atas TX ke 13V.

Langkah 8: Kesimpulan

Spice sangat pandai mengungkapkan "rahasia tersembunyi" dari operasi sirkuit. Jelas rangkaian JDM bekerja dan kompatibel dengan banyak chip PIC, tetapi pengamatan berikut mengungkapkan kemungkinan keterbatasan/masalah kompatibilitas/kesalahan?

- Waktu naik yang lama dari MCLR sementara C2 mengisi daya ke VPP pada pulsa pertama TX. Spesifikasi gagal 3.

- Port serial mengisi C2 saat TX menjadi tinggi dan RTS menjadi rendah. Tetapi RTS juga memiliki tugas untuk mengisi daya C3. Ketika keduanya terjadi pada saat yang sama ini menciptakan lebih banyak beban pada RTS, akibatnya C3 kehilangan muatan (VSS naik) pada 2ms pada simulasi. Spesifikasi gagal 1.

- C3 kehilangan muatan (VSS mulai naik) setelah pulsa clock berhenti pada 3.5ms.

- Apa tujuan dari C2, dibutuhkan sama sekali?

Solusi

- Agaknya PICPgm menggunakan perangkat lunak "work-round". Itu harus menerapkan pulsa TX panjang untuk mengisi daya ke C2, lalu hanya masuk ke mode pemrograman setelah pulsa TX kedua? Untuk simulasi saya mengurangi nilai C2 ke 1uF untuk memberikan waktu naik 1ms. Bukan solusi ideal.

- Pisahkan C2 dan C3 sehingga mereka mengisi daya secara independen. Satu modifikasi kecil untuk JDM2, C2 dirujuk ke GND bukan VSS.

- Dipecahkan oleh JDM3. ICSP jauh lebih andal karena PIC ditenagai oleh rangkaian target.

- JDM4 memecahkan masalah 1. Ini adalah desain langsung yang menghilangkan C2 sama sekali.

Langkah 9: Dan Akhirnya

Buktinya puding ada di makan. JDM ini berfungsi, jadi lanjutkan menggunakannya.

Dan rekomendasi saya adalah:

- gunakan JDM2 untuk pemrograman soket dan port serial 12V,

- gunakan JDM4 untuk programmer ICSP dan port serial di atas +/-9V,

- gunakan JDM4 dengan jumper X2 dihapus untuk port serial di atas +/-7V.

Referensi:

Perangkat Analog LT bumbu

picpgm

Fruttenboel

Ikuti lebih banyak proyek PIC di sly-corner

Direkomendasikan:

Ulasan Elegoo Super Started Kit Uno R3: 4 Langkah

Elegoo Super Started Kit Uno R3 Ulasan: Beberapa hari yang lalu Elegoo mengirimi saya Super Starter Kit ini untuk pengujian. Jadi, mari kita lihat apa yang ada di dalamnya. Saat membuka casing kompak ini, kita bisa melihat banyak barang. Di sampul ada indeks dengan semua komponen. Di dalamnya kami memiliki kartu ucapan terima kasih dengan semua

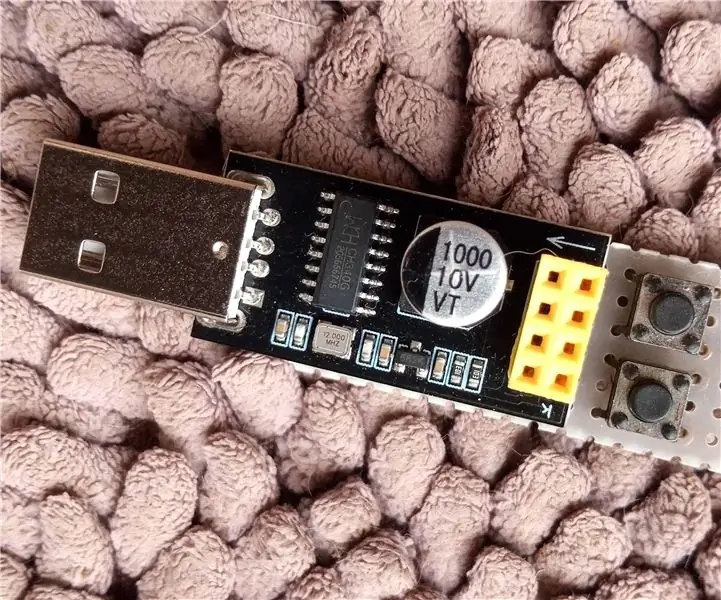

Hack Programmer ESP-01 - Yang Mudah :): 6 Langkah

ESP-01 Programmer Hack - Yang Mudah :): Hai ESPers,Dalam instruksi ini saya akan menunjukkan kepada Anda hack sederhana untuk membuat programmer untuk modul ESP-01 / ESP8266-01 / ES-01. Sebagian besar dari kita telah menggunakan papan Arduino atau perangkat FTDI USB-TTL sebagai pemrogram untuk modul ini. Kedua metode bekerja dengan baik. Tapi t

Cara Flash atau Program Firmware ESP8266 AT Dengan Menggunakan Flasher dan Programmer ESP8266, Modul Wifi IOT: 6 Langkah

Cara Flashing atau Program Firmware ESP8266 AT Dengan Menggunakan Flasher dan Programmer ESP8266, Modul Wifi IOT : Keterangan :Modul ini merupakan USB adapter/programmer untuk modul ESP8266 tipe ESP-01 atau ESP-01S. Ini dilengkapi dengan header perempuan 2x4P 2.54mm untuk menyambungkan ESP01. Ini juga mematahkan semua pin ESP-01 melalui h

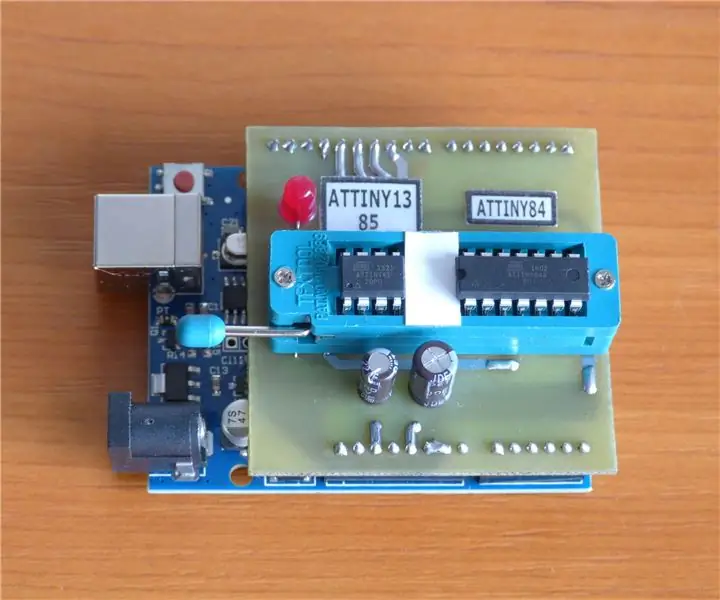

Programmer Kecil untuk Mikrokontroler ATTINY Dengan Arduino UNO: 7 Langkah

Pemrogram Kecil untuk Mikrokontroler ATTINY Dengan Arduino UNO: Saat ini menarik untuk menggunakan mikrokontroler seri ATTINY karena keserbagunaannya, harganya yang murah tetapi juga fakta bahwa mereka dapat dengan mudah diprogram di lingkungan seperti Arduino IDE. Program yang dirancang untuk modul Arduino dapat dengan mudah mentransfer

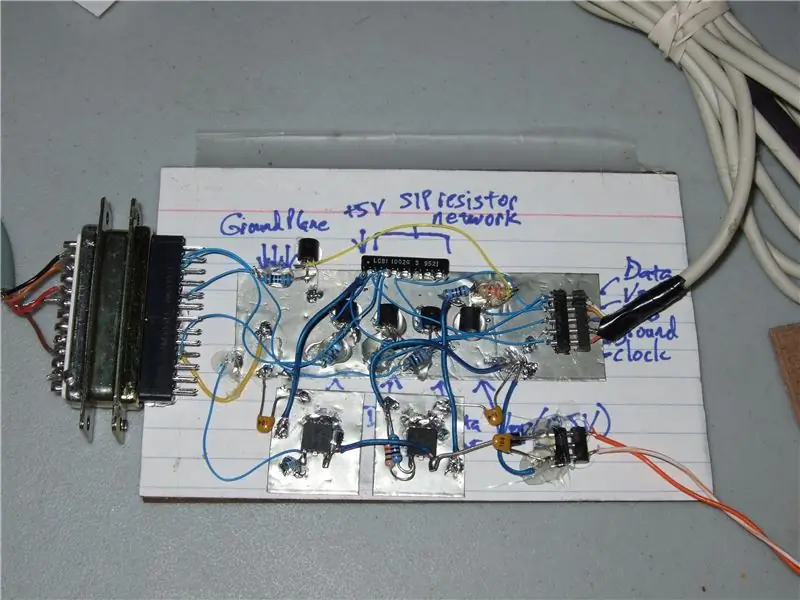

5 Transistor PIC Programmer *Skematis Ditambahkan ke Langkah 9!: 9 Langkah

5 Transistor PIC Programmer *Skematis Ditambahkan ke Langkah 9!: Buat programmer PIC Anda sendiri untuk port paralel komputer Anda. Ini adalah variasi dari desain klasik David Tait. Ini sangat andal dan ada perangkat lunak pemrograman bagus yang tersedia secara gratis. Saya suka programmer IC-Prog dan PICpgm. Terbaik dari semua, itu