Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:55.

- Terakhir diubah 2025-01-23 14:49.

Hubungkan papan pengembangan Mojo Anda ke input eksternal dengan pelindung ini.

Apa itu papan pengembangan Mojo?

Papan pengembangan Mojo adalah papan pengembangan yang berbasis di sekitar Xilinx spartan 3 FPGA. Papan dibuat oleh Alchitry. FPGA sangat berguna di mana banyak proses harus dijalankan secara bersamaan.

Apa yang akan Anda butuhkan?

Perlengkapan

Papan pengembangan Mojo

File Gerber

Resistor 8 x 15k ohm (opsional*)

4x470 ohm resistor

4x560 ohm resistor

4 x CC tujuh segmen menampilkan

4x3mm LED

4 x sakelar taktil SPDT

1 x 4 posisi permukaan mount DIP switch

2 x 25 kali 2 atau 4 x 25 tajuk

1x 2 kali 5 pin kotak kepala

Besi solder

Pateri

Aliran

*(jika resistor ini dihilangkan pullup/pulldown internal harus diaktifkan untuk pin yang relevan)

Langkah 1: Unggah Gerber ke Produsen Pcb Pilihan Anda

Untuk papan saya, saya memesan dari JLC PCB.

Satu-satunya perubahan yang saya buat adalah warna yang saya ingin cocokkan dengan warna hitam Mojo.

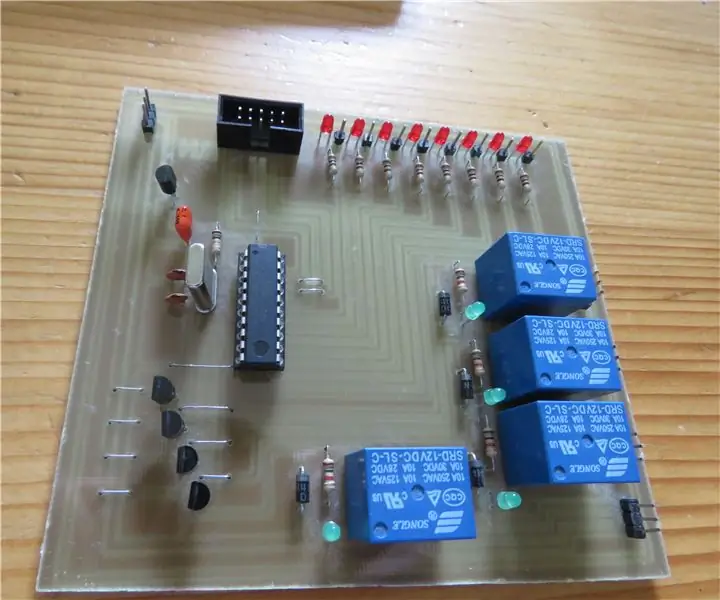

Langkah 2: Majelis Dewan

Saat menyolder, saya selalu merasa berguna untuk menyolder bagian terendah terlebih dahulu sehingga memulai dengan resistor adalah ide yang bagus.

R5, R6, R7, R8, R9, R10, R11 dan R12 adalah resistor 15k ohm yang digunakan untuk menurunkan sakelar (jika Anda menggunakan pullup/pulldown internal, abaikan ini).

R1, R2, R3, R4 adalah resistor 560 ohm yang bertanggung jawab untuk membatasi arus melalui tampilan 7 segmen.

R13, R14, R15, R16 adalah resistor 470 ohm yang bertanggung jawab untuk membatasi arus melalui 4 LED.

Selanjutnya solder sakelar celup, sakelar taktil, LED, display tujuh segmen, dan konektor header kotak dalam urutan itu.

Sekarang tempatkan 25 kali 2 (atau 2 25 kali 1) ke dalam mojo untuk menyelaraskan pin. Sejajarkan pelindung dengan pin dan solder di tempatnya.

Langkah 3: Pengaturan Perangkat Lunak

Untuk perangkat lunak yang merujuk ke situs web Alchitry akan memberi tahu Anda apa yang Anda butuhkan untuk memulai dan menginstal Xilinx ISE. Namun mengubah file.ucf sehingga tahu pin apa yang terhubung ke apa yang penting untuk menjalankan program Anda.

Berikut adalah file.ucf yang saya gunakan dengan perisai:

KONFIG VCCAUX=3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODE "clk" 50 MHz TINGGI 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q[0]" LOC = P26 | IOSTANDARD = LVTTL; BERSIH "Q[1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q[2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q[3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S[0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S[1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S[2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S[3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb[1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb[2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb[3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb[4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega[0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb[0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc[0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd[0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege[0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf[0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg[0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp[0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega[1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb[1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc[1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd[1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege[1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf[1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg[1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp[1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega[2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb[2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc[2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd[2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege[2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf[2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg[2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp[2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega[3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb[3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc[3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd[3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege[3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf[3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg[3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp[3]" LOC = P121 | IOSTANDARD = LVTTL;

Ingat jika Anda belum memasang resistor pulldown untuk mengedit pin di.ucf dengan

| TARIK; Hai

| TARIK;

Jika Anda ingin menggunakan blok untuk apa pun, koneksinya adalah sebagai berikut. Kiri menjadi nomor pin blok dan kanan adalah nomor pin mojo yang harus Anda tetapkan di.ucf Anda:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Direkomendasikan:

Pengembangan Papan Drivemall: 5 Langkah

Pengembangan Papan Drivemall: Dalam tutorial ini kita akan melihat langkah-langkah dasar untuk membuat papan Arduino kustom. Perangkat lunak yang digunakan adalah KiCad untuk desain papan dan Arduino IDE untuk pembuatan dan pemuatan firmware untuk papan

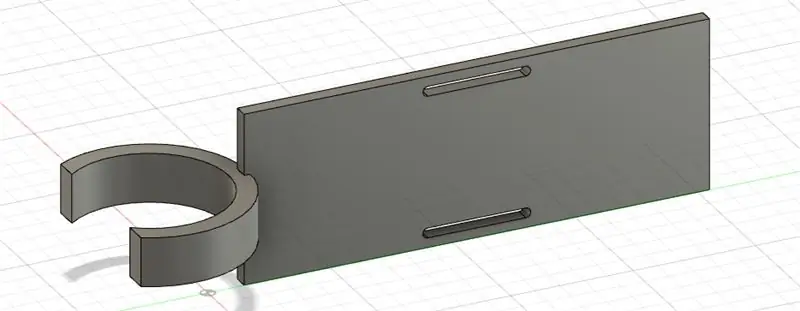

Vokal GOBO - Perisai Peredam Suara - Booth Vokal - Kotak Vokal - Filter Refleksi - Perisai Vokal: 11 Langkah

Vokal GOBO - Perisai Peredam Suara - Booth Vokal - Kotak Vokal - Filter Refleksi - Perisai Vokal: Saya mulai merekam lebih banyak vokal di studio rumah saya dan ingin mendapatkan suara yang lebih baik dan setelah beberapa penelitian saya menemukan apa itu "GOBO" NS. Saya telah melihat hal-hal peredam suara ini tetapi tidak benar-benar menyadari apa yang mereka lakukan. Sekarang saya lakukan. saya menemukan y

Papan Pengembangan ESP32 DIY - ESPer: 5 Langkah (dengan Gambar)

Papan Pengembangan ESP32 DIY - ESPer: Jadi baru-baru ini saya membaca tentang banyak IoT (Internet of Things) dan percayalah, saya tidak sabar untuk menguji salah satu perangkat luar biasa ini, dengan kemampuan untuk terhubung ke internet, sendiri dan mendapatkan pekerjaan saya. Beruntung kesempatan

Membuat Papan Pengembangan Sendiri Dengan Mikrokontroler: 3 Langkah (dengan Gambar)

Buat Papan Pengembangan Anda Sendiri Dengan Mikrokontroler: Apakah Anda pernah ingin membuat papan pengembangan sendiri dengan mikrokontroler dan Anda tidak tahu caranya. Dalam instruksi ini saya akan menunjukkan cara membuatnya. Yang Anda butuhkan hanyalah pengetahuan dalam elektronik, merancang sirkuit dan pemrograman. Jika Anda memiliki quest

Bermain Game Flappy Bird Dengan Papan Pengembangan M5stick C Berbasis M5stack Esp32: 5 Langkah

Bermain Game Flappy Bird Dengan Papan Pengembangan M5stick C Berbasis M5stack Esp32: Hai teman-teman hari ini kita akan belajar cara mengunggah kode permainan burung flappy ke papan pengembangan m5stick c yang disediakan oleh m5stack. Untuk proyek kecil ini, Anda memerlukan dua hal berikut: m5stick-c papan pengembangan: https://www.utsource.net/itm/p/8663561.h