Daftar Isi:

- Langkah 1: Blok Diagram

- Langkah 2: Prinsip Operasi

- Langkah 3: Implementasi Logika

- Langkah 4: Menyelesaikan Kebuntuan

- Langkah 5: Konfigurasi Perangkat - Sirkuit Matrix0

- Langkah 6: Konfigurasi Perangkat - SPI Clocking Logic

- Langkah 7: Konfigurasi Perangkat - Properti Komponen Matrix0

- Langkah 8: Konfigurasi Perangkat - Sirkuit Matrix1

- Langkah 9: Konfigurasi Perangkat - Penghitung Biner 3-bit

- Langkah 10: Konfigurasi Perangkat - Logika Perbandingan 3-bit

- Langkah 11: Konfigurasi Perangkat - Logika Perbandingan Digital dan Register Sementara

- Langkah 12: Konfigurasi Perangkat - Properti Komponen Matrix1

- Langkah 13: Hasil

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:54.

- Terakhir diubah 2025-01-23 14:49.

Sistem kontrol dan perangkat terkait berurusan dengan beberapa sumber daya, seperti garis bias atau baterai, dan harus melacak garis tertinggi (atau terendah) di antara rangkaian yang diberikan.

Misalnya, pengalihan beban dalam sistem bertenaga "multi baterai" mengharuskan sistem memantau tegangan minimum atau maksimum di antara susunan baterai (maks atau min sebagai fungsi dari algoritme pengalihan tertentu) dan secara dinamis merutekan beban ke sumber yang paling tepat secara real time. Sebagai alternatif, sistem mungkin perlu untuk sementara memutuskan sambungan baterai bertegangan terendah untuk pengisian yang benar.

Contoh lain adalah sistem tenaga surya modern, di mana setiap panel surya dilengkapi dengan mekanisme tiltrotate dan dengan sirkuit pelacakan surya (yang terakhir memberikan informasi posisi Matahari untuk mengarahkan panel). Dengan info tegangan maksimum, setiap posisi panel surya dapat disetel dengan baik berdasarkan panel string yang benar-benar menghasilkan tegangan output tertinggi, sehingga mencapai tingkat optimalisasi daya yang unggul.

Ada beberapa merek IC komersial yang berbeda (terutama mikrokontroler) yang pada prinsipnya dapat menerapkan pengikut tegangan maksimum. Namun, mereka membutuhkan pemrograman dan kurang hemat biaya daripada solusi sinyal campuran. Melengkapi desain Dialog GreenPAKTM dapat secara positif mempengaruhi keterjangkauan, ukuran, dan modularitas desain. Desain ini memanfaatkan manfaat mengintegrasikan sirkuit analog dan digital ke dalam satu chip tunggal.

Dalam Instruksi ini, ujung depan analog dan logika digital yang diperlukan untuk mengimplementasikan pencari tegangan maks (atau akhirnya min) di antara delapan sumber berbeda diimplementasikan.

Untuk menerapkan monitor tegangan maks/mnt analog 8 saluran, digunakan SLG46620G.

Di bawah ini kami menjelaskan langkah-langkah yang diperlukan untuk memahami bagaimana solusi telah diprogram untuk membuat monitor tegangan maks/mnt analog 8 saluran. Namun, jika Anda hanya ingin mendapatkan hasil pemrograman, unduh perangkat lunak GreenPAK untuk melihat File Desain GreenPAK yang sudah selesai. Colokkan GreenPAK Development Kit ke komputer Anda dan tekan program untuk membuat monitor tegangan maks/mnt analog 8 saluran.

Langkah 1: Blok Diagram

Gambar 1 menunjukkan diagram global dari sistem yang diimplementasikan.

Sebuah string hingga 8 sumber tegangan variabel digandakan dan dihubungkan ke modul ADC GreenPAK yang terhubung ke desain internal yang disesuaikan yang mampu memilih sumber dengan tegangan tertinggi sehubungan dengan yang lain. Logika internal mengeluarkan informasi ini untuk ditampilkan atau diproses lebih lanjut.

Desain didasarkan pada produk GreenPAK SLG46620G, karena menyematkan semua blok bangunan analog dan digital yang diperlukan untuk aplikasi. Dalam implementasi ini array dipindai dengan menggunakan multiplexer analog ADG508 yang langsung digerakkan oleh IC GreenPAK.

Informasi keluaran adalah nomor digital 3-bit yang sesuai dengan nomor sumber tegangan pada tegangan maksimum. Cara langsung untuk mendapatkan informasi ini adalah dengan menunjukkan nomor melalui tampilan 7-segmen. Ini dapat dengan mudah dicapai dengan menghubungkan output digital SLG46620G ke driver tampilan 7-segmen, seperti solusi GreenPAK yang dijelaskan dalam Referensi atau ke IC 74LS47 umum.

Rangkaian yang disajikan mencari tegangan maksimum. Untuk mengubah desain menjadi pencari tegangan minimum, rangkaian pra-kondisi sederhana harus ditambahkan antara multiplexer analog dan input analog GreenPAK, mengurangi output multiplexer dari tegangan referensi 1 V.

Langkah 2: Prinsip Operasi

Desain bertujuan untuk memilih sumber dengan tegangan maksimum, oleh karena itu pemindaian dilakukan pada seluruh array sambil menyimpan nilai maksimum terakhir dan membandingkannya dengan nilai input berikutnya (yang termasuk sumber tegangan berikutnya dalam pemindaian).

Berikut ini kita akan mengacu pada urutan multiplexing lengkap sepanjang semua input sebagai "scan" atau "loop".

Perbandingan antara dua nilai tidak dilakukan melalui komponen ACMP (namun, tersedia di SLG46620G), melainkan oleh modul DCMP, setelah nilai masing-masing didigitalkan. Ini adalah teknik canggih dan halus yang pertama kali dibahas dalam Referensi.

Gambar 2 menunjukkan bagaimana SLG46620G disusun untuk desain ini.

Sinyal input analog masuk ke input ADC melalui komponen PGA dengan satu set Penguatan 1. Berbagai pengaturan Penguatan juga dimungkinkan untuk menemukan kecocokan terbaik dengan elektronik pengkondisian front-end yang dikhususkan untuk memetakan tegangan input ke 0-1 V jangkauan modul ADC GreenPAK.

ADC beroperasi dalam mode ujung tunggal dan mengubah sinyal analog menjadi kode digital 8-bit, yang kemudian ditransfer ke modul DCMP. Kode digital juga dimasukkan ke dalam blok SPI, dikonfigurasi sebagai Buffer ADC/FSM, di mana kode digital dapat disimpan dan tidak akan berubah hingga pulsa berikutnya masuk ke input SPI CLK. Perhatikan bahwa blok logika khusus menggerakkan input SPI CLK. Kami akan menyelidiki bagian ini nanti, karena ini adalah logika "inti" yang bertanggung jawab untuk operasi yang benar. Kode digital baru disimpan ke dalam modul SPI hanya jika itu milik tegangan input maks yang sebenarnya.

Komponen DCMP digunakan untuk membandingkan data ADC saat ini dengan pemenang terakhir (yaitu maksimum terakhir yang ditemukan) yang disimpan di blok SPI. Ini akan menghasilkan pulsa pada output OUT+ ketika data ADC baru lebih besar dari yang sebelumnya. Kami menggunakan sinyal OUT+ untuk memperbarui blok SPI dengan pemenang baru.

Sinyal jam global mendorong konversi ADC dan pengaturan waktu umum. Setelah konversi dilakukan, sinyal output INT ADC berdenyut, dikoordinasikan dalam waktu dengan output data paralel ADC. Kami menggunakan output INT juga untuk menambah penghitung biner 3-bit, yang diimplementasikan oleh DFF di Matrix1, yang berguna karena tiga alasan:

1. Jalur keluaran penghitung menangani multiplekser analog eksternal, sehingga melayani tegangan masukan berikutnya ke ADC;

2. Hitungan dibekukan ke dalam register 3-bit (diimplementasikan dalam Matrix1) untuk menyimpan pemenang sementara selama pemindaian;

3. Hitungan didekodekan untuk memperbarui register 3-bit kedua (diimplementasikan dalam Matrix0) setelah pemindaian selesai.

Langkah 3: Implementasi Logika

Modul ADC secara berurutan menyediakan data yang dikonversi dari semua tegangan input, satu demi satu, tanpa batas. Setelah Multiplexer dialamatkan 0b111 (desimal 7), penghitung bergulir ke 0b000 (desimal 0) sehingga memulai pemindaian baru dari tegangan input.

Selama pemindaian, sinyal output ADC INT dihasilkan ketika output data paralel valid. Ketika sinyal ini berdenyut, multiplexer analog harus beralih ke input berikutnya, memberikan PGA tegangan yang sesuai. Oleh karena itu, output ADC INT adalah sinyal clocking langsung dari Penghitung Biner 3-bit pada Gambar 2, yang kata keluaran paralel 3-bitnya secara langsung mengalamatkan multiplexer analog eksternal (“V pilih” pada Gambar 1).

Mari kita lihat contoh di mana tegangan input seharusnya memiliki hubungan berikut:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

Gambar 3 merupakan sinyal utama yang terlibat dalam mekanisme max-decision.

Karena data akhirnya di-clock ke register buffer SPI secara sinkron dengan pulsa INT, jendela perbandingan ada di mana konten buffer SPI dibandingkan dengan hasil konversi ADC berikutnya. Waktu khusus ini menghasilkan pembangkitan pulsa OUT+ pada output DCMP. Kita dapat memanfaatkan pulsa ini untuk memuat nilai baru ke dalam register buffer SPI.

Seperti terlihat dari jalur data buffer SPI pada Gambar sebelumnya, register SPI selalu berisi, dari waktu ke waktu, nilai terbesar di antara 8 input dan diperbarui hanya ketika nilai yang lebih besar terdeteksi oleh modul DCMP (mengacu pada DCMP OUT+ garis output plot, pulsa yang hilang menyebabkan V2 tetap terkunci di register sampai dibandingkan dengan V5).

Langkah 4: Menyelesaikan Kebuntuan

Jika logika yang diterapkan akan seperti yang dijelaskan di atas, jelas bahwa kita akan menghadapi situasi kebuntuan: sistem hanya mampu mendeteksi tegangan yang lebih tinggi dari tegangan yang sesuai dengan apa yang disimpan ke dalam register buffer SPI.

Ini juga berlaku jika tegangan ini akan turun dan kemudian input lain, sampai sekarang lebih rendah dari itu, menjadi yang tertinggi: tidak akan pernah terdeteksi. Situasi ini lebih baik dijelaskan pada Gambar 4 di mana hanya 3 tegangan input yang ada untuk kepentingan kejelasan.

Pada saat iterasi 2, V3 turun dan V1 adalah tegangan maks aktual. Tetapi modul DCMP tidak memberikan pulsa karena data yang disimpan ke register buffer SPI (berhubungan dengan 0,6 V) lebih besar daripada yang sesuai dengan V1 (0,4 V).

Sistem kemudian berperilaku sebagai pencari maks "mutlak" dan tidak memperbarui output dengan benar.

Cara yang bagus untuk mengatasi masalah ini adalah dengan memaksa memuat ulang data ke dalam Daftar Penyangga SPI ketika sistem menyelesaikan siklus pemungutan suara penuh dari semua saluran.

Faktanya, jika tegangan pada input tersebut masih tertinggi, tidak ada perubahan dan kontrol berjalan dengan aman (mengacu pada Gambar 4 di atas, ini adalah kasus Loop Iterasi 0 dan 1). Di sisi lain, jika tegangan pada input itu secara kebetulan turun ke nilai yang lebih kecil dari input lain, maka reload nilai tersebut memberikan kemungkinan kepada modul DCMP untuk menghasilkan pulsa OUT+ ketika membandingkannya dengan nilai maks yang baru (ini adalah kasus Loop Iterasi 2 dan 3).

Sepotong rangkaian logika diperlukan untuk mengatasi masalah tersebut. Itu harus menghasilkan sinyal clock ke komponen SPI ketika loop mencapai input maks yang sebenarnya, sehingga memaksa memuat ulang kata data yang diperbarui ke dalam Daftar Penyangga SPI. Ini akan dibahas dalam Bagian 7.2 dan 7.6 di bawah ini.

Langkah 5: Konfigurasi Perangkat - Sirkuit Matrix0

SLG46620G memiliki dua blok Matrix, seperti yang digambarkan pada Gambar 2. Gambar berikut menunjukkan konfigurasi perangkat masing-masing.

Bagian atas sirkuit adalah "Loop Register" yang direalisasikan dengan 3 DFF (DFF0, DFF1, dan DFF2). Itu disegarkan setelah setiap loop dari multiplexer input untuk mengirim ke driver tampilan 7-segmen nomor biner dari "pemenang", yaitu input dengan tegangan tertinggi dalam pemindaian terakhir. Baik jam ke DFF maupun data berasal dari logika yang diimplementasikan di Matrix1 melalui port P12, P13, P14, dan P15.

Bagian bawah adalah ujung depan analog dengan input pada Pin 8 dan PGA dengan gain x1. Keluaran ADC INT berjalan baik ke logika clocking SPI dan ke Matrix1 melalui port P0, di mana ia akan berfungsi sebagai sinyal clock untuk penghitung yang diimplementasikan.

Output data paralel ADC dan SPI masing-masing diberi label NET11 dan NET15 untuk dihubungkan ke komponen DCMP di Matrix1.

Langkah 6: Konfigurasi Perangkat - SPI Clocking Logic

Seperti yang ditunjukkan sebelumnya di bagian “Implementasi Logika”, Daftar Penyangga SPI diperbarui setiap kali perbandingan antara nilai tersimpan aktual dan data konversi ADC baru menghasilkan pulsa pada keluaran DCMP OUT+.

Integritas sinyal dipastikan jika sinyal ini AND-ed dengan output ADC INT. Ini menghindari lonjakan dan pemicu palsu.

Kami juga telah menggarisbawahi bahwa untuk melewati situasi kebuntuan, Buffer SPI harus diperbarui ketika loop mencapai data pemenang yang sebenarnya.

Tiga sinyal kemudian ada dalam permainan untuk pencatatan jam kerja SPI yang tepat:

1. Keluaran ADC INT (LUT0-IN1)

2. Keluaran DCMP OUT+ (LUT0-IN0 melalui port P10)

3. Hitung sama dengan sinyal Latch (LUT0-IN2 melalui port P11)

Dua yang pertama adalah AND-ed dan keduanya OR-ed dengan yang terakhir di LUT0, yang implementasinya dikonfigurasi seperti pada Gambar 6.

Langkah 7: Konfigurasi Perangkat - Properti Komponen Matrix0

Gambar 7-10 menunjukkan jendela properti komponen yang tersisa milik Matrix0.

Langkah 8: Konfigurasi Perangkat - Sirkuit Matrix1

Langkah 9: Konfigurasi Perangkat - Penghitung Biner 3-bit

Bagian atas rangkaian berisi elemen logika, terutama penghitung biner 3-bit yang di-clock oleh output ADC INT, seperti yang telah dibahas. Penghitung ini diimplementasikan dengan skema yang cukup “standar” yang ditunjukkan pada Gambar 12.

Penghitung ini diwujudkan dalam desain kami melalui Flip-Flops DFF9, DFF10, DFF11 dan INV1, LUT4, LUT8. Output DFF9 adalah LSB sedangkan DFF11 adalah MSB seperti yang ditunjukkan pada Gambar 13.

LUT4 dikonfigurasi sebagai XOR sementara LUT8 menjalankan logika AND-XOR pada Gambar 12.

Keluaran penghitung pergi ke tiga pin keluaran digital untuk mengatasi Multiplexer Analog eksternal.

LUT10 mendekode kode penghitung saat pemindaian selesai dan mengumpankan pulsa ke Matrix0 melalui DLY8 dan port P12. Ini hanya dilakukan dengan AND-ing output counter, sehingga decoding nomor 7 dec (biner 0b111, akhir loop).

Langkah 10: Konfigurasi Perangkat - Logika Perbandingan 3-bit

Gambar 15 menunjukkan rangkaian yang digunakan untuk mendeteksi ketika loop sedang berulang pada alamat "pemenang" saat ini. Dalam hal ini, seperti yang telah dibahas, pulsa digital harus memaksa memuat ulang hasil ADC saat ini untuk memecahkan kemungkinan situasi kebuntuan.

Alamat "pemenang" disimpan dalam register sementara Matrix1 (lihat di bawah), sedangkan alamat saat ini dikeluarkan oleh penghitung biner.

Gerbang XNOR memberikan output yang benar (logika 1 atau 'tinggi') ketika kedua input sama. AND-ing sinyal ini untuk semua bit (LUT9) memberi kita pulsa ketika kedua kode biner sama. Detail tentang gerbang XOR sebagai pemeriksa paritas dapat ditemukan di Referensi.

Sinyal 'Counter-equals-Latch' diteruskan ke Matrix0 melalui port P11.

Langkah 11: Konfigurasi Perangkat - Logika Perbandingan Digital dan Register Sementara

Bagian bawah Gambar 11 (disorot pada Gambar 16) menunjukkan blok DCMP, bagian pengambilan keputusan dari desain ini.

DFF6, 7, dan 8 membentuk register 3-bit untuk menyimpan nomor input sementara "pemenang" saat loop sedang berjalan. Input ke Flip-Flops adalah output pencacah biner 3-bit, seperti yang terlihat di sirkuit Matrix1 global Gambar 11, di sini dilewati demi kejelasan.

Keluaran register ini tidak dapat mengarahkan secara langsung tampilan 7-segmen karena nilai yang disimpan di sini berubah selama pemindaian dan harus dianggap 'valid' hanya pada akhir pemindaian itu sendiri.

Untuk alasan ini, output register sementara terhubung ke Register Loop Matrix0 melalui port antar-matriks P13, P14, dan P15.

Penting untuk diperhatikan pada Gambar 16 bahwa register sementara di-clock oleh output DCMP OUT+ ketika register ADC-SPI menghasilkan perbandingan maks baru yang ditemukan.

Sinyal OUT+ yang sama diteruskan ke Matrix0, SPI CLK Logic, melalui port P10.

Langkah 12: Konfigurasi Perangkat - Properti Komponen Matrix1

Gambar 17-19 menunjukkan jendela properti komponen milik Matrix1.

Langkah 13: Hasil

Untuk menguji implementasinya, telah dibangun prototipe papan evaluasi, dimana 8 tegangan input analog diperoleh dari rangkaian pembagi resistor dengan TrimPots (seperti yang ditunjukkan pada Gambar 20).

Multiplexer yang digunakan adalah ADG508, bagian yang dapat beroperasi dengan suplai tunggal (12 V).

Driver tampilan 7-segmen adalah 74LS47. Ini menerjemahkan kata input paralel dan secara langsung menggerakkan tampilan 7-segmen common-anode.

Papan evaluasi memiliki konektor sudut kanan 2x10 untuk dihubungkan langsung ke GreenPAK Advanced Development Platform pada konektor ekspansi seperti yang ditunjukkan pada Gambar 21.

Penggabungan dengan GreenPAK Advanced Development Platform membuatnya sangat mudah untuk melakukan pengukuran sinyal untuk pemeriksaan cepat. Misalnya, Gambar 22 menunjukkan sekumpulan sinyal (masing-masing CLOCK, output ADC INT, dan output DCMP OUT+) seperti yang ditangkap oleh HP 54620A Logic Analyzer. Bentuk gelombang dipicu oleh naiknya tepi sinyal OUT+ (pada cakupan berlabel 'A>B'), oleh karena itu ini adalah penangkapan bentuk gelombang ketika Tegangan maks baru terdeteksi di antara input analog. Sebenarnya, itu diperoleh dengan memutar salah satu TrimPot dari Papan Evaluasi untuk meningkatkan tegangan yang sesuai yang ditunjukkan pada Gambar 22.

Gambar 23 menunjukkan skema Dewan Evaluasi.

Kesimpulan

Dalam Instruksi ini, kami menerapkan pencari tegangan maksimum (atau min) delapan saluran untuk digunakan sebagai tambahan umum untuk sistem kontrol multi-saluran. Pendekatan yang disajikan memanfaatkan fitur-fitur canggih dari komponen GreenPAK dan menunjukkan bagaimana mungkin untuk mengintegrasikan dalam satu chip tunggal fungsi analog dan digital. Beberapa IC komersial dapat diganti dengan Dialog GreenPAK sehingga ukuran aplikasi dan biaya dapat dikurangi.

Direkomendasikan:

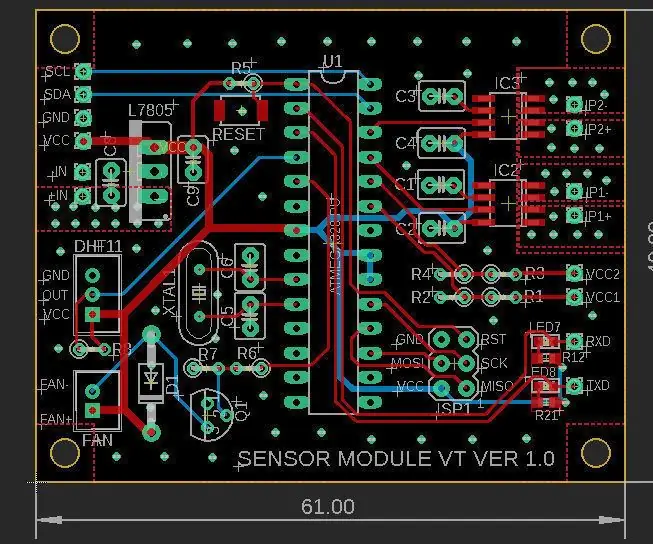

Modul Sensor Tegangan Saluran Ganda Arduino: 8 Langkah

Modul Sensor Tegangan Saluran Ganda Arduino: Sudah beberapa tahun sejak saya menulis instruksi, saya berpikir inilah saatnya untuk kembali. Saya telah lama ingin membangun sensor tegangan sehingga saya dapat terhubung ke catu daya bangku saya. Saya memiliki catu daya variabel dua saluran, ia memiliki n

Monitor Tegangan untuk Baterai Tegangan Tinggi: 3 Langkah (dengan Gambar)

Monitor Tegangan untuk Baterai Tegangan Tinggi: Dalam panduan ini saya akan menjelaskan kepada Anda bagaimana saya membuat monitor tegangan baterai untuk longboard listrik saya. Pasang sesuka Anda dan sambungkan hanya dua kabel ke baterai Anda (Gnd dan Vcc). Panduan ini mengasumsikan bahwa tegangan baterai Anda melebihi 30 volt, w

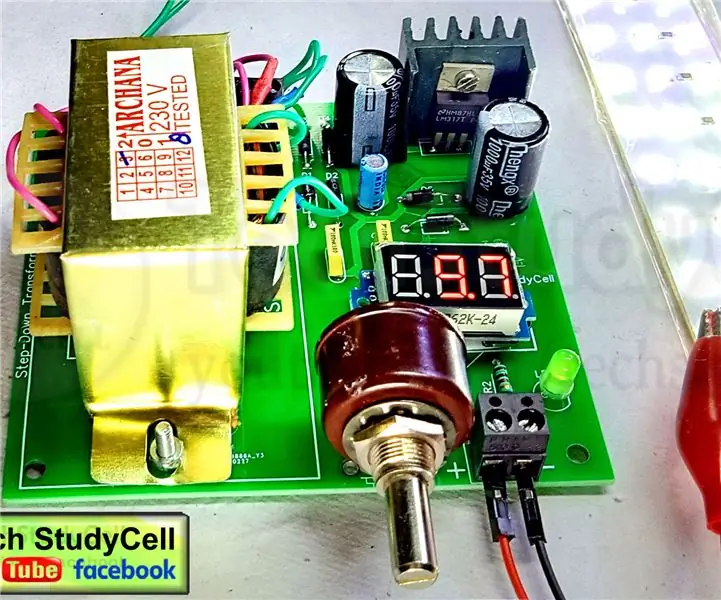

Catu Daya DC Tegangan Disesuaikan Menggunakan Regulator Tegangan LM317: 10 Langkah

Catu Daya DC Tegangan Disesuaikan Menggunakan Regulator Tegangan LM317: Pada proyek ini, saya telah merancang catu daya DC tegangan sederhana yang dapat disesuaikan menggunakan IC LM317 dengan diagram rangkaian catu daya LM317. Karena rangkaian ini memiliki penyearah jembatan bawaan sehingga kita dapat langsung menghubungkan suplai AC 220V/110V pada input

Antena Indoor BIQUAD, Terbuat dari Tembaga dan Kayu untuk Penerimaan Saluran HDTV di Pita UHF (SALURAN 14-51): 7 Langkah

Antena Indoor BIQUAD, Terbuat dari Tembaga dan Kayu untuk Penerimaan Saluran HDTV di Pita UHF (SALURAN 14-51): Di pasaran terdapat berbagai macam antena untuk televisi. Yang paling populer menurut kriteria saya adalah: UDA-YAGIS, Dipole, Dipole with reflector, Patch dan antena Logarithmic. Tergantung pada kondisinya, jarak dari transmisi

Termometer Digital Berbasis Picaxe Dengan Maks dan Min: 13 Langkah

Termometer Digital Berbasis Picaxe Dengan Max dan Min: (Silakan tinggalkan pesan, tetapi jangan terlalu kritis, ini adalah instruksi pertama saya!!) Ini adalah termometer yang saya buat untuk van kemping kami, untuk menunjukkan suhu eksternal. Ini didasarkan pada chip Picaxe karena murah dan mudah digunakan. Jika ini untuk