Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:53.

- Terakhir diubah 2025-01-23 14:49.

Dalam tutorial ini, kita akan menggunakan FPGA untuk mengontrol rangkaian LED eksternal. Kami akan mengimplementasikan tugas-tugas berikut:

(A) Gunakan tombol tekan pada FPGA Cyclone IV DuePrologic untuk mengontrol LED.

(B) LED Flash hidup & mati secara berkala

Video demo

Menu lab:

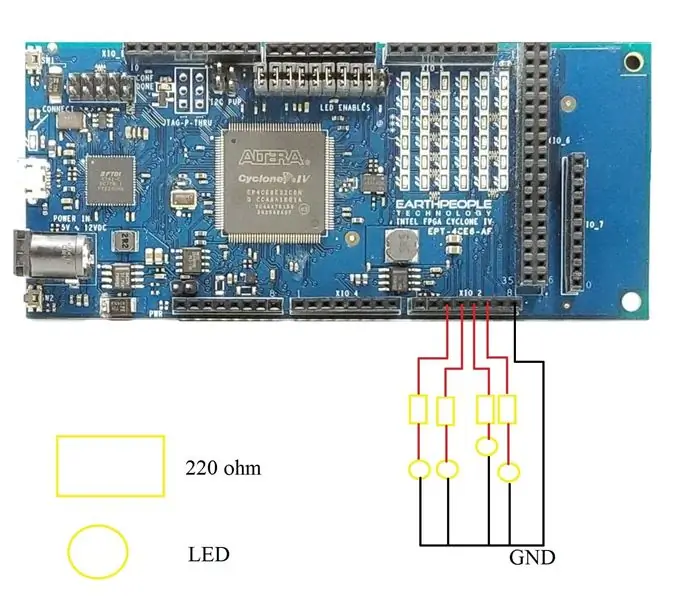

Langkah 1: Bangun Sirkuit Elektronik

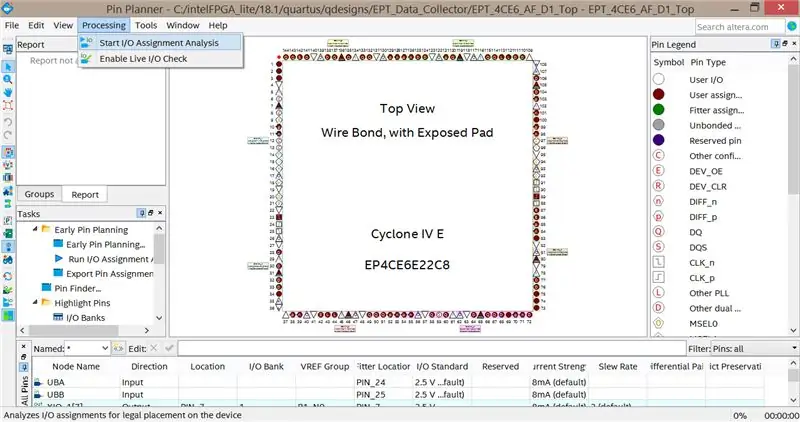

Langkah 2: Periksa Pin Planner dan Edit Kode Verilog

Langkah 3: Edit Kode Verilog

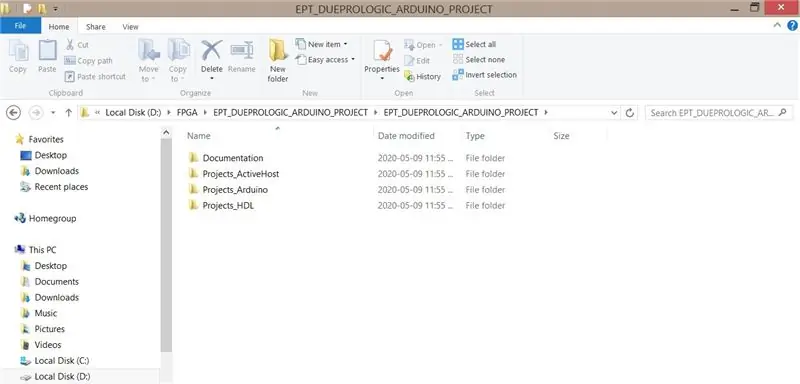

Saat Anda membeli FPGA DueProLogic, Anda akan menerima DVD. Setelah Anda membuka "Projects_HDL", Anda akan melihat file kode asli

Tambahkan kode yang disorot. Ini mendaftarkan port I/O dan menetapkan nomor ke port.

kabel keluaran [7:0] XIO_1, //XIO -- D2-D9

kabel keluaran [5:0] XIO_2, //XIO -- D10-D12

kabel keluaran [5:0] XIO_3, //XIO -- D22-D29

kabel masukan [5:0] XIO_4, //XIO -- D30-D37

kabel masukan [5:0] XIO_5, //XIO -- D38-D45

kabel keluaran [4:0] XIO_6_OUT, //XIO -- D46-D53

kabel masukan [31:5] XIO_6, //XIO -- D46-D53

kabel keluaran [2:0] XIO_7, //XIO -- D69, D70, D71, D74, D75, D76

kabel input UBA, // Sakelar Tombol Tekan

kabel input UBB // Saklar Tombol Tekan

tetapkan XIO_1[3] = start_stop_cntrl;

tetapkan XIO_2[1] = start_blinky; //LED flash LED hidup dan mati

tetapkan XIO_2[2] = 1'b1; //keluaran TINGGI

menetapkan XIO_2[3] = ~UBA; //Tekan tombol A

tetapkan XIO_2[4] = UBB; //Tekan tombol B

tetapkan c_enable = XIO_5[2];

menetapkan LEDExt = XIO_5[5];

Kemudian kita harus mengatur waktu tunda. Komentari kode pengatur waktu asli dan tulis fungsi pengatur waktu baru

//-----------------------------------------------

// LED Berkedip mulai

//-----------------------------------------------

/*

selalu @(posedge CLK_66 atau negedge RST)

mulai

jika(!RST)

start_blinky <= 1'b0;

lain

mulai

jika(control_register[7:4] > 0)

start_blinky <= 1'b1;

lain

start_blinky <= 1'b0;

akhir

akhir

*/

reg [31:0] contoh;

awal mulai

contoh <= 32'b0;

start_blinky <= 1'b0;

akhir

selalu @(berpose CLK_66)

mulai

ex <= ex + 1'b1;

if(ex > 100000000) //flash hidup/mati ~1,6 detik, jam 66MHz

mulai

start_blinky <= !start_blinky;

contoh <= 32'b0;

akhir

akhir

//-----------------------------------------------

// Penghitung Waktu Tunda LED

//-----------------------------------------------

/*

selalu @(posedge CLK_66 atau negedge RST)

mulai

jika(!RST)

led_delay_counter <= TIMER_LOW_LIMIT;

lain

mulai

jika(status[SELECT_MODE])

led_delay_counter <= nilai_waktu;

else if(status[WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

akhir

akhir*/

Langkah 4: Kompilasi Kode Verilog

Tekan "Mulai Kompilasi" di Quartus, tidak ada pesan kesalahan yang harus dibuat.

Jika Anda menerima pesan kesalahan tentang beberapa pin. Buka Tugas -> Perangkat -> Opsi Perangkat dan Pin -> Pin Dual-Purpose -> ubah nilai pin yang sesuai menjadi "Gunakan sebagai I/O biasa".

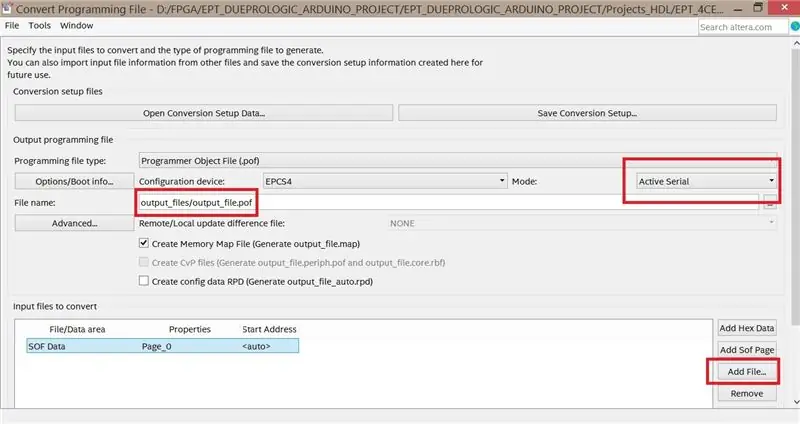

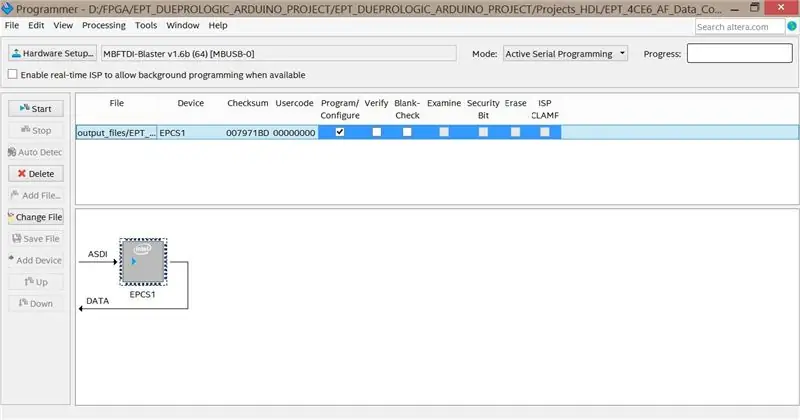

Setelah kompilasi, Anda harus mendapatkan file output pof secara langsung. Jika perangkat lunak Anda tidak mutakhir, Anda mungkin hanya mendapatkan file lunak. Ketika itu terjadi, klik "File" di Quartus -> "convert programming files". Ubah pengaturan yang ditandai dengan kotak merah.

Langkah 5: Ayo Coba

Bagaimanapun, itu harus berhasil!!! LED kuning selalu menyala. LED merah berkedip. LED biru mati jika Anda menekan tombol B. LED hijau menyala jika Anda menekan tombol A

Direkomendasikan:

FPGA Cyclone IV DueProLogic Mengontrol Kamera Raspberry Pi: 5 Langkah

FPGA Cyclone IV DueProLogic Mengontrol Kamera Raspberry Pi: Meskipun FPGA DueProLogic secara resmi dirancang untuk Arduino, kita akan membuat FPGA dan Raspberry Pi 4B dapat dikomunikasikan. Tiga tugas diimplementasikan dalam tutorial ini:(A) Tekan dua tombol tekan secara bersamaan pada FPGA untuk membalik sudut

FPGA Cyclone IV DueProLogic Mengontrol Motor Servo: 4 Langkah

FPGA Cyclone IV DueProLogic Mengontrol Motor Servo: Dalam tutorial ini, kita akan menulis kode Verilog untuk mengontrol motor servo. Servo SG-90 diproduksi oleh Waveshare. Saat Anda membeli motor servo, Anda mungkin menerima lembar data yang mencantumkan tegangan operasi, torsi maksimum, dan Pu

Game Arkade LED Cyclone: 4 Langkah

Cyclone LED Arcade Game: Tujuan dari proyek ini adalah untuk membuat game sederhana menggunakan Arduino yang interaktif dan menghibur untuk anak-anak. Saya ingat game arcade Cyclone menjadi salah satu game arcade favorit saya ketika saya masih muda, jadi saya memutuskan untuk menirunya. T

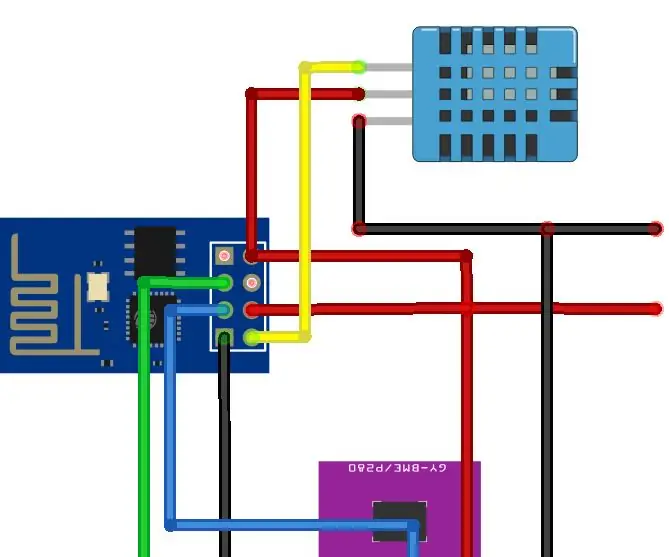

Satu Lagi Stasiun Cuaca Arduino (ESP-01 & BMP280 & DHT11 & OneWire): 4 Langkah

Satu Lagi Stasiun Cuaca Arduino (ESP-01 & BMP280 & DHT11 & OneWire): Di sini Anda dapat menemukan satu iterasi menggunakan OneWire dengan sedikit pin ESP-01. Perangkat yang dibuat dalam instruksi ini terhubung ke jaringan Wifi Anda pilihan (Anda harus memiliki kredensial…)Mengumpulkan data sensorik dari BMP280 dan DHT11

Bor Tekan Laser Pointer: 3 Langkah (dengan Gambar)

Bor Tekan Laser Pointer: Apa yang terjadi ketika Anda menambahkan $40 Laser dan $10 membantu tangan ke bor tekan?Setelah mengebor sekelompok papan sirkuit, saya sampai pada kesimpulan bahwa harus ada cara yang lebih baik untuk melakukan latihan target. Jadi saya memesan laser pointer dan