Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:54.

- Terakhir diubah 2025-01-23 14:49.

Oleh AmCoderhttps://www.linkedin.com/in/mituIkuti Penulis lainnya:

Tentang: Mitu Raj -- Sekedar Hobi dan Pembelajar -- Desainer Chip -- Pengembang Perangkat Lunak -- Penggemar Fisika dan Matematika Selengkapnya Tentang AmCoder »

##Ini adalah tautan yang paling banyak diklik dan populer di Google untuk implementasi VHDL dari ALGORITMA CORDIC untuk menghasilkan gelombang sinus dan kosinus## Saat ini, banyak algoritma yang efisien perangkat keras ada, tetapi ini tidak dikenal karena dominasi sistem perangkat lunak atas bertahun-tahun. CORDIC adalah suatu algoritma yang tidak lain adalah satu set logika pergeseran dan penambahan yang digunakan untuk menghitung berbagai fungsi termasuk fungsi trigonometri, hiperbolik, linier dan logaritmik tertentu. Ini adalah algoritma yang digunakan dalam kalkulator dll. Jadi hanya dengan menggunakan shifter dan adder sederhana kita dapat merancang perangkat keras dengan lebih sedikit kompleksitas tetapi kekuatan DSP menggunakan algoritma cordic. Oleh karena itu dapat dirancang sebagai desain RTL telanjang di VHDL atau Verilog tanpa menggunakan unit floating point khusus atau IP matematika yang kompleks.

Langkah 1: VHDL dan Modelsim

Di sini algoritma cordic diimplementasikan menggunakan VHDL untuk menghasilkan gelombang sinus dan gelombang cose. Ini dapat menghasilkan sinus dan kosinus sudut input dengan presisi tinggi. Kode ini dapat disintesis pada FPGA. Modelsim digunakan untuk mensimulasikan desain dan bangku tes.

Langkah 2: Kode VHDL untuk Desain dan Bangku Tes

Teknik penskalaan biner digunakan untuk merepresentasikan bilangan floating point.

Silakan buka dokumen terlampir sebelum Anda membuat kode.

Pergi melaluiSimulating cordic_v4.vhd - Desain -Inputnya adalah sudut dalam 32 bit + bit tanda; itu dapat memproses sudut apa pun dari 0 hingga +/-360 derajat dengan presisi input 0,000000000233 derajat. Saat memberikan input -> MSB adalah bit tanda dan 32 bit sisanya mewakili magnitudo.-Output dari desain adalah nilai sinus dan cos dalam 16 bit + bit tanda.ie; dengan presisi 0,00001526. Harap dicatat bahwa output ditampilkan dalam bentuk pujian 2 jika nilai sinus atau cos masing-masing negatif. Simulasi testb.vhd - Test Bench Untuk Desain (1) Sudut input dan tarik reset ='0'. Setelah dua langkah simulasi tarik reset ke '1' dan " jalankan semua ".(2) Pada jendela simulasi atur radix sinyal sin dan cos sebagai desimal dan format > Analog (otomatis).(3) Perkecil untuk melihat bentuk gelombang dengan baik.

Langkah 3: File Terlampir

(1) cordic_v4.vhd - Desain.(2) testb.vhd - Bangku uji untuk desain.

(3) Dokumen tentang cara memaksa input sudut dan mengonversi hasil biner.

Pembaruan: FILE INI SUDAH Usang DAN TIDAK DISEDIAKAN LAGI. HARAP GUNAKAN FILE DARI LANGKAH BERIKUTNYA

Langkah 4: Inti IP Mini-Cordic - 16 Bit

Keterbatasan implementasi di atas adalah- lambat, frekuensi clock operasi lebih rendah karena melakukan komputasi dalam satu siklus clock. Core IP Mini-Cordic - 16 Bit

- Jalur kritis didistribusikan ke beberapa siklus untuk meningkatkan kinerja.- Lebih cepat - Desain terbukti FPGA disintesis hingga 100 Mhz clock.- Lebih banyak area yang dioptimalkan dalam HDL, Perangkat keras yang lebih sedikit.- Sinyal Load and Done Status ditambahkan.- Satu-satunya downside adalah resolusi yang lebih rendah dibandingkan dengan sebelumnya. Testbench:

sepenuhnya otomatis dari input sudut 0 hingga 360 derajat

File Terlampir:1) file vhdl utama mini cordic2) bangku tes mini cordic3) manual Mini Cordic IP Core4) Dokumen tentang cara memaksa sudut dan mengonversi hasil

Untuk setiap pertanyaan, jangan ragu untuk menghubungi saya:

Mitu Raj

ikuti saya:

email: iammituraj@gmail.com

###Total unduhan: 325 hingga 01-05-2021###

### Kode terakhir diedit: Juli-07-2020 ###

Direkomendasikan:

Robot Penyeimbang Diri - Algoritma Kontrol PID: 3 Langkah

Self Balancing Robot - Algoritma Kontrol PID: Proyek ini dibuat karena saya tertarik untuk mempelajari lebih lanjut tentang Algoritma Kontrol dan bagaimana menerapkan loop PID fungsional secara efektif. Proyek ini masih dalam tahap pengembangan karena modul Bluetooth belum ditambahkan yang akan

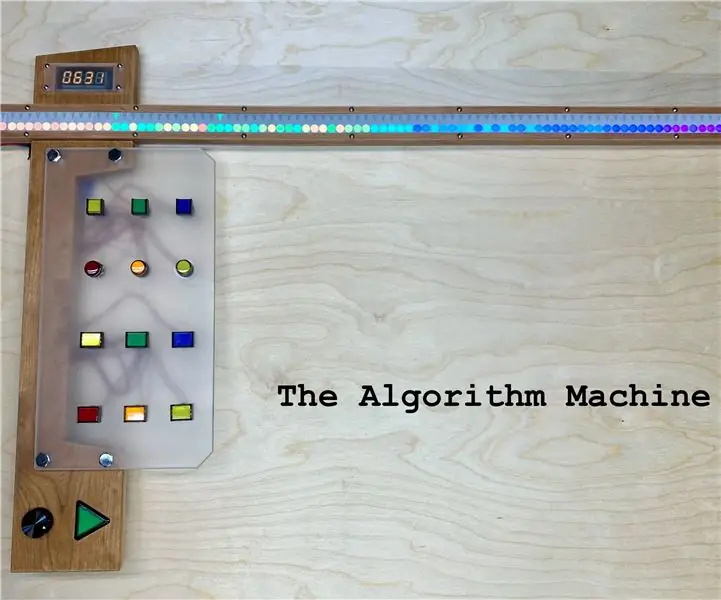

Mesin Algoritma: 13 Langkah (dengan Gambar)

Mesin Algoritma: Saya telah mengajar ilmu komputer di tingkat perguruan tinggi selama 15 tahun, dan meskipun keahlian saya lebih pada sisi pemrograman, saya masih menghabiskan cukup banyak waktu untuk membahas algoritma standar untuk pencarian dan pengurutan. Dari sisi pengajaran

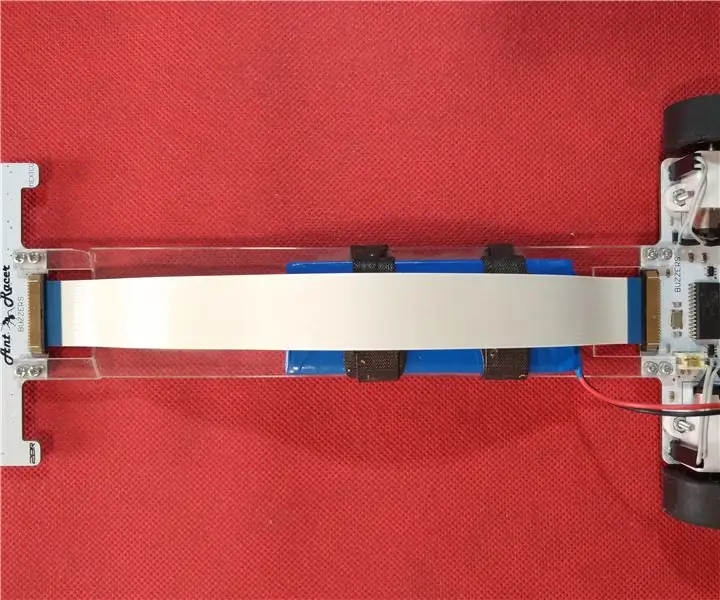

Robot Pengikut Garis untuk Algoritma Kontrol Pengajaran: 3 Langkah

Robot Pengikut Garis untuk Algoritma Kontrol Pengajaran: Saya merancang robot pengikut garis ini beberapa tahun yang lalu ketika saya masih menjadi guru robotika. Tujuan dari proyek ini adalah untuk mengajari siswa saya cara membuat kode robot mengikuti garis untuk kompetisi dan juga membandingkan antara kontrol If/Else dan PID. Dan tidak

Robot Self Balancing Menggunakan Algoritma PID (STM MC): 9 Langkah

Self Balancing Robot Menggunakan PID Algorithm (STM MC): Baru-baru ini banyak pekerjaan telah dilakukan dalam self balancing objek. Konsep keseimbangan diri dimulai dengan keseimbangan pendulum terbalik. Konsep ini diperluas ke desain pesawat juga. Dalam proyek ini, kami telah merancang mod kecil

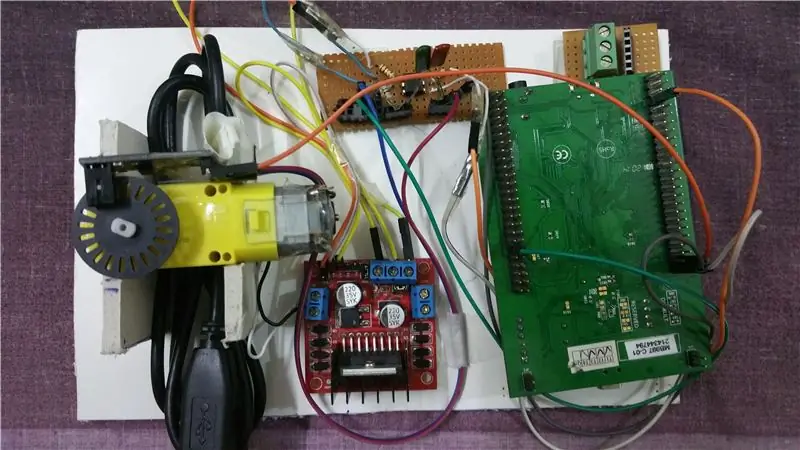

Kontrol Kecepatan Motor DC Menggunakan Algoritma PID (STM32F4): 8 Langkah (dengan Gambar)

Kontrol Kecepatan Motor DC Menggunakan Algoritma PID (STM32F4): halo semuanya,Ini tahir ul haq dengan proyek lain. Kali ini STM32F407 sebagai MC. Ini adalah proyek akhir semester. Semoga Anda menyukainya. Ini membutuhkan banyak konsep dan teori, jadi kita masuk dulu. Dengan munculnya komputer dan