Daftar Isi:

- Langkah 1: Pengoperasian Pengguna Digital Sequencer

- Langkah 2: Detail Teknis

- Langkah 3: Detail Teknis

- Langkah 4: Pembagi Jam 7-segmen

- Langkah 5: Pembagi Jam Ketukan Per Menit

- Langkah 6: Pitch Pembagi Jam

- Langkah 7: Mainkan/Jeda/Pilih Mesin Status

- Langkah 8: Mainkan/Jeda/Pilih Mesin Status

- Langkah 9: Keluarkan FSM

- Langkah 10: Keluarkan FSM

- Langkah 11: Catatan Tugas

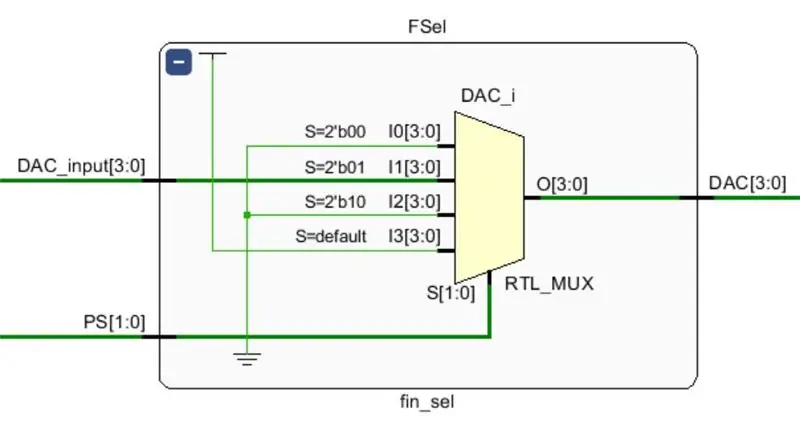

- Langkah 12: Pilih Output

- Langkah 13: Gen Gelombang Persegi

- Langkah 14: Tampilan 7-segmen

- Langkah 15: Pilihan Terakhir

- Langkah 16: Perangkat Eksternal: DAC

- Langkah 17: Perangkat Eksternal: Speaker

- Langkah 18: Demo Video

- Langkah 19: Kode VHDL

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:58.

- Terakhir diubah 2025-01-23 14:49.

CPE 133, Cal Poly San Luis Obispo

Pembuat Proyek: Jayson Johnston dan Bjorn Nelson

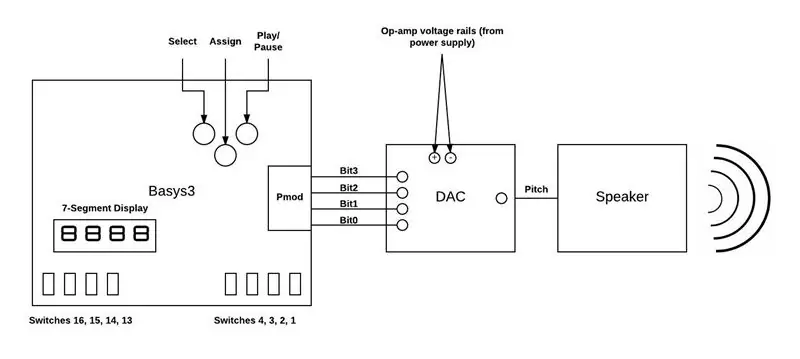

Dalam industri musik saat ini, salah satu "instrumen" yang paling umum digunakan adalah synthesizer digital. Setiap genre musik, dari hip-hop hingga pop dan bahkan country, menggunakan synthesizer digital di studio untuk menciptakan ketukan dan suara yang mereka butuhkan untuk menghidupkan musik mereka. Dalam tutorial ini, kita akan membuat synthesizer yang sangat sederhana dengan papan Basys 3 FPGA.

Synthesizer akan dapat memainkan empat not seperempat yang dipilih dengan jumlah ketukan per menit yang konstan. Pengguna akan menggunakan sakelar untuk menetapkan setiap not seperempat ke nada musik. Untuk proyek ini kami menggunakan 4-bit digital to analog converter (DAC) untuk mengambil output dari board dan mengubahnya menjadi sinyal analog. Output dari DAC kemudian akan diumpankan ke speaker komputer standar, menciptakan musik kami. Enam belas nada diskrit dimungkinkan. Kami akan membatasi synthesizer kami ke satu oktaf dari 12 nada, yang berada di antara C tengah (261,6 Hz) dan B4 (493,9 Hz). Pengguna juga akan memiliki opsi untuk menetapkan beberapa nada secara bersamaan, serta menetapkan istirahat dengan menekan assign sementara tidak ada tombol pitch yang bergeser ke atas. Saat setiap not dipilih dan dimainkan, not huruf ditampilkan pada tampilan 7-segmen. Kami juga akan menggunakan tiga tombol di papan, satu untuk memutar dan menjeda musik, satu untuk mengatur ulang synthesizer dan memasukkannya ke mode "pilihan", dan yang ketiga untuk menetapkan nada setiap nada saat dalam mode pemilihan.

Setelah pengguna puas dengan pilihan nadanya, dan setelah menekan tombol putar, penyintesis akan memainkan setiap nada secara berurutan berulang kali hingga pengguna menekan jeda atau pilih.

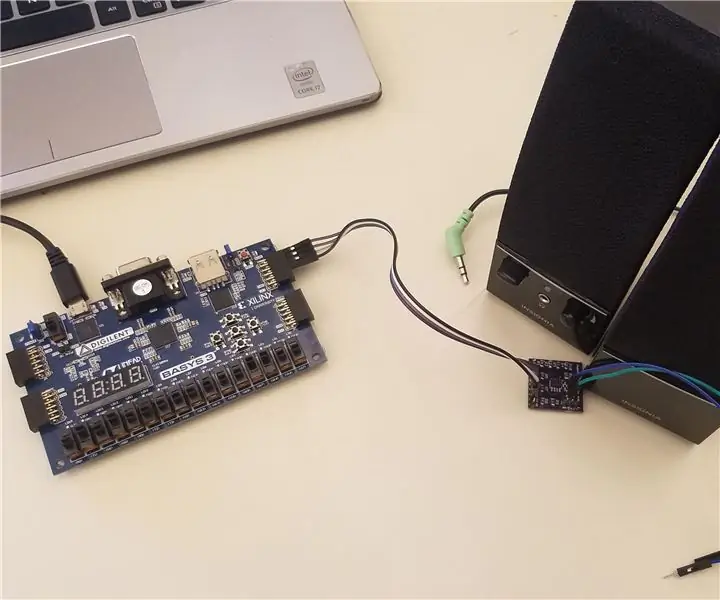

Berikut daftar peralatan yang dibutuhkan:

- Vivado (atau ruang kerja VHDL apa pun)

- Basys 3 atau papan FPGA serupa

- Konverter digital ke analog (min. 4-bit)

- Speaker dengan jack headphone

- Kawat mengarah

Langkah 1: Pengoperasian Pengguna Digital Sequencer

Langkah-langkah berikut adalah mengoperasikan sequencer digital. Sequencer digital mendukung pemutaran 12 nada berbeda (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), yang berkisar dari 261,6 Hz hingga 493,9 Hz.

1. Tekan tombol kiri untuk memasukkan papan ke mode pemilihan. Saat dalam mode ini, 4 sakelar paling kiri (sakelar 13 hingga 16) masing-masing akan digunakan untuk menyimpan nilai nada yang berbeda.

2. Untuk membuat pilihan, aktifkan salah satu sakelar kiri, lalu gunakan 4 sakelar paling kanan (sakelar 1 hingga 4) untuk memilih nada yang diinginkan. Pitch yang terkait dengan kombinasi spesifik sakelar kanan akan ditampilkan pada tampilan tujuh segmen, dan tampilan akan diperbarui ke pitch terkait baru setiap kali sakelar kanan digeser ke kombinasi baru. Istirahat dapat ditetapkan dengan tidak pernah menetapkan nada ke salah satu sakelar kiri, atau dengan menetapkan nada yang ditunjukkan sebagai 0 pada tampilan pada not. Setelah nada yang diinginkan ditemukan dan ditampilkan di layar, tekan tombol tetapkan bawah untuk menetapkan nada tertentu ke nada.

3. Ulangi langkah 2 untuk tiga nada yang tersisa, dengan membalik masing-masing sakelar kiri yang tersisa satu per satu, memilih nada masing-masing dengan sakelar kanan, dan menekan tombol bawah untuk menetapkan nada ke nada. Beberapa nada dapat diberi nada yang sama dengan menggeser lebih dari satu tombol kiri ke atas secara bersamaan.

4. Sekarang setelah semua nada nada telah ditetapkan, sequencer digital siap dimainkan. Untuk memutar not di speaker, cukup tekan tombol putar/jeda kanan untuk mulai memutar musik. Urutan urutan pemutaran mencerminkan nada yang terkait dengan sakelar kiri, dari kiri ke kanan. Catatan akan dimainkan pada jumlah ketukan per menit, dalam urutan 1, 2, 3, 4, 1, 2…. Layar akan menampilkan not yang sedang diputar saat speaker memutar musik. Untuk menjeda pemutaran musik, cukup tekan tombol kanan, lalu musik akan berhenti diputar dan simbol jeda akan ditampilkan di layar. Menekan tombol kanan lagi akan melanjutkan pemutaran.

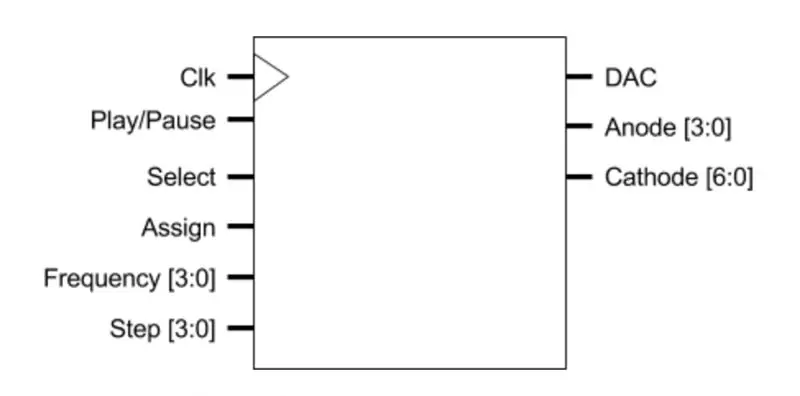

Langkah 2: Detail Teknis

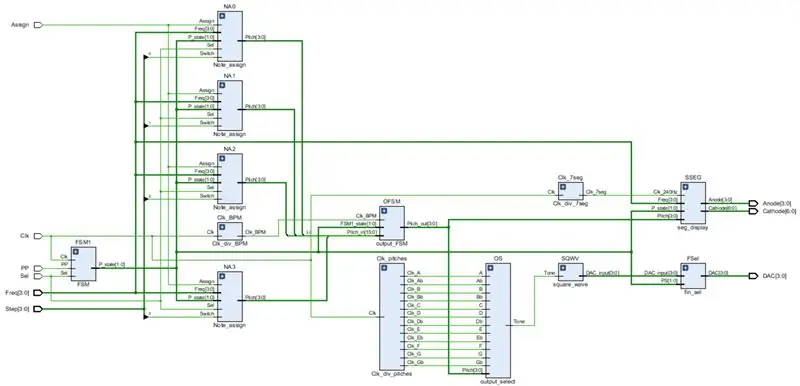

Synthesizer kami menggunakan banyak komponen digital yang berbeda. Termasuk adalah mesin keadaan terbatas, register, multiplexer, pembagi jam dan banyak lagi. Untuk membangun synthesizer kami, kami menggunakan 10 file modular unik. Daripada membuat setiap modul menjadi komponen, kami memecah file modular berdasarkan fungsi. Kebanyakan modul, sebagai hasilnya, lebih dari satu komponen. Perhatikan gambar di atas menunjukkan setiap blok diikat bersama dalam desain teratas kami.

Kami akan membahas setiap modul dengan menjelaskan input dan output, merinci komponennya, dan menjelaskan tujuannya dalam desain keseluruhan. File ZIP disertakan di bagian bawah instruksi, yang berisi setiap file kode VHDL yang digunakan dalam proyek.

Masukan

- Clk (sinyal jam asli)

- PP (putar/jeda)

- Sel (menempatkan synthesizer dalam mode pemilihan)

- Tetapkan (tetapkan langkah ke nada)

- Langkah (catatan posisi)

- Freq (saklar menciptakan nada yang diinginkan)

Keluaran

- Anoda (anoda 7 segmen)

- Katoda (katoda 7 segmen)

- DAC (4-bit menggerakkan DAC)

Langkah 3: Detail Teknis

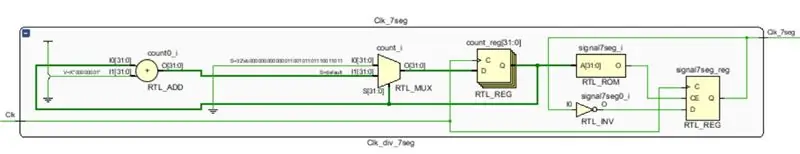

Langkah 4: Pembagi Jam 7-segmen

Synthesizer kami menggunakan tiga pembagi jam, semuanya menghasilkan sinyal yang melayani tujuan berbeda dalam proyek kami. Pembagi jam mengambil sinyal jam asli dan menghasilkan sinyal yang diubah yang memiliki frekuensi lebih kecil dari sinyal jam asli. Jam asli Basys 3 adalah 100 MHz. Ini adalah frekuensi yang digunakan oleh pembagi jam kami. Jika Anda menggunakan papan FPGA yang berbeda dengan frekuensi jam asli yang berbeda, Anda mungkin harus mengubah kodenya.

Pembagi jam 7-segmen menghasilkan sinyal yang menggerakkan file seg_display. Kami akan menjelaskan bagaimana file ini bekerja secara lebih rinci ketika kita sampai ke bagiannya. Pada dasarnya, pembagi jam ini menghasilkan sinyal 240 Hz yang akan digunakan untuk beralih antara anoda dan katoda pada layar. Sinyalnya adalah 240 Hz karena frekuensi di mana mata manusia tidak dapat mengenali ketiadaan cahaya adalah 60 Hz. Kami menggunakan dua digit, jadi dengan menggandakan frekuensi ini, setiap digit akan berosilasi pada 60 Hz. Kemudian kita gandakan untuk mendapatkan 240 Hz karena sistem hanya berubah saat sinyalnya tinggi, bukan saat sinyalnya rendah.

Untuk mencapai ini, pembagi mengambil sinyal asli 100 MHz dan menghitung di setiap tepi naik. Ketika penghitung mencapai 416667, output akan berubah dari rendah ke tinggi, atau sebaliknya.

Masukan

Clk (sinyal jam asli)

Keluaran

Clk_7seg (untuk seg_display)

Komponen

- D mendaftar

- MUX

- Inverter

- penambah

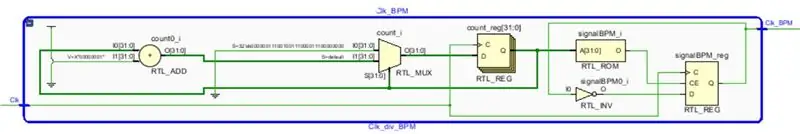

Langkah 5: Pembagi Jam Ketukan Per Menit

Pembagi jam BPM bekerja dengan cara yang sama. Pembagi ini menghasilkan frekuensi clock yang mendorong peralihan antara empat langkah saat mengeluarkan nada dalam status putar. Kami memutuskan untuk beralih antar not pada 100 BPM. Pada 100 BPM, setiap not akan dimainkan selama 3/5 detik. Sinyal yang dihasilkan akan memiliki frekuensi 1,67 Hz.

Untuk menghasilkan sinyal frekuensi ini, kami kembali menggunakan sistem pencacahan, tetapi kali ini hitungannya adalah 60 juta. Setiap kali penghitung mencapai 60 juta, sinyal output akan beralih tinggi atau rendah.

Masukan

Clk (frekuensi jam asli)

Keluaran

Clk_BPM (ke output_FSM)

Komponen

- D daftar

- MUX

- Inverter

- penambah

Langkah 6: Pitch Pembagi Jam

Pembagi Jam Pitch adalah pembagi jam terbesar kami. Pembagi ini menghasilkan 12 sinyal berbeda yang sesuai dengan 12 nada berbeda yang dapat dimainkan oleh synthesizer kami. Menggunakan pengetahuan dasar teori musik, kami menyimpulkan bahwa bit atau bus dapat berosilasi pada tingkat yang sesuai dengan frekuensi not musik. Untuk melihat frekuensi yang kami gunakan, lihat di sini. Kami menggunakan nada oktaf keempat.

Sistem penghitungan yang sama digunakan di sini. Untuk nilai spesifik yang kami hitung, lihat file berlabel Clk_div_pitches.

Masukan

Clk (frekuensi jam asli)

Keluaran

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (untuk output_select)

Komponen

- D mendaftar

- MUX

- Inverter

- penambah

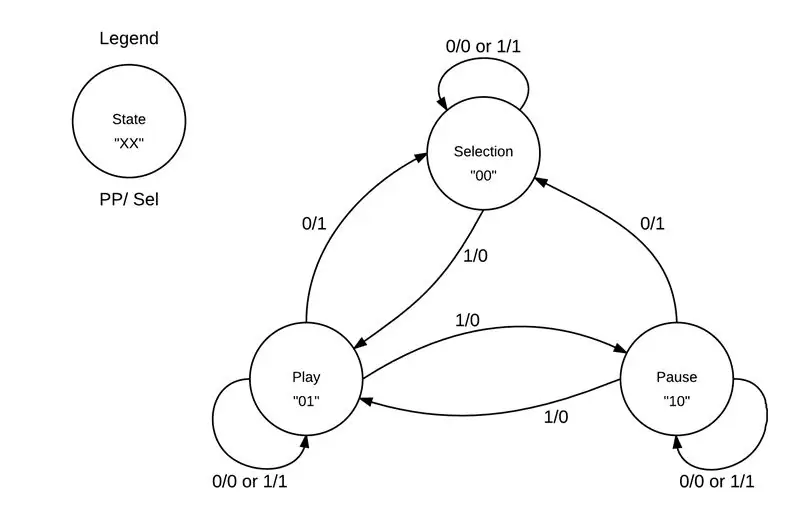

Langkah 7: Mainkan/Jeda/Pilih Mesin Status

Dalam proyek kami ada dua finite state machine (FSM). FSM adalah perangkat logika yang dapat eksis hanya dalam satu keadaan dari sejumlah keadaan yang terbatas. Menggunakan FSM, sirkuit digital dapat berpindah ke keadaan baru berdasarkan kombinasi input. Menggunakan logika input, keadaan FSM akan berubah ketika ada peningkatan jam. Dari keadaan dan masukan ke dalam rangkaian, Anda dapat membuat logika keluaran yang memberikan keluaran yang hanya ada jika FSM dalam keadaan tertentu.

Mesin status PPS adalah FSM pertama di sirkuit kami. Ada tiga negara bagian dalam FSM ini; Putar, Jeda, dan mode Pilihan. Untuk berpindah melalui status yang berbeda, kami menggunakan tombol PP dan Seleksi. Lihat diagram keadaan di atas untuk melihat bagaimana transisi antar keadaan terjadi. Kami membuat transisi FSM ini pada tepi naik dari jam asli 100 MHz, sehingga tidak mungkin mesin tidak melakukan transisi ketika salah satu tombol ditekan, bahkan untuk waktu yang sangat singkat. Status saat ini (P_state) adalah satu-satunya keluaran dari modul ini.

Masukan

- Clk (frekuensi jam asli)

- Sel (tombol kiri)

- PP (tombol kanan)

Keluaran

P_state (status sekarang, ke output_FSM, note_assign, seg_dsiplay, final_select)

Komponen

- MUX

- D daftar

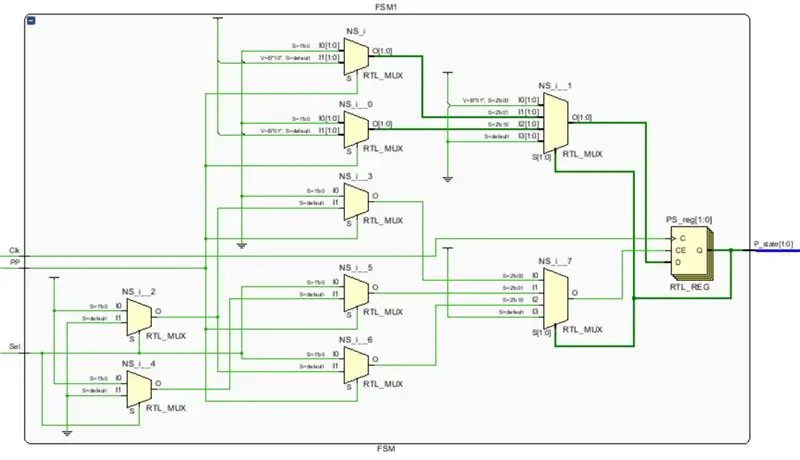

Langkah 8: Mainkan/Jeda/Pilih Mesin Status

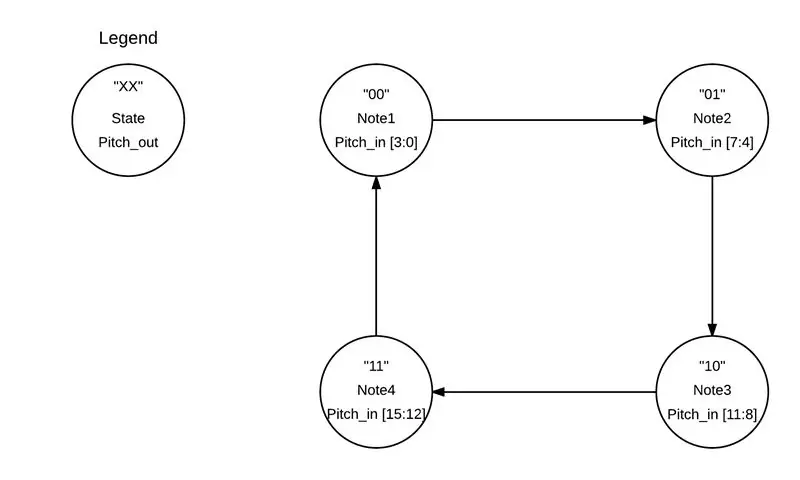

Langkah 9: Keluarkan FSM

Ini adalah FSM kedua yang dirujuk di bagian sebelumnya. FSM ini memiliki fungsi yang berbeda dari yang lain, tetapi dasar untuk yang satu ini pada dasarnya sama.

Output FSM hanya beroperasi jika status sekarang dari FSM pertama adalah "01" (status putar). Pada dasarnya, ini adalah pengaktifan untuk modul. Jika statusnya adalah "01", maka FSM akan beralih antar status di tepi naik sinyal clock BPM. Kami melakukan ini karena output_FSM mengontrol nomor biner mana untuk nada terpilih yang dikirim ke modul output_select dan seg_display. FSM memiliki input 16-bit yang berasal dari modul penetapan catatan, yang akan dibahas selanjutnya. Dalam status "00" untuk output_FSM, modul akan menampilkan "xxxx" untuk nada pertama yang ditetapkan. Kemudian di "01", itu akan menampilkan "yyyy" untuk nada kedua dan seterusnya untuk setiap nada sebelum bergulir kembali ke nada pertama. Lihat diagram keadaan di atas.

FSM ini berbeda dari yang pertama karena tidak ada logika input untuk mengontrol peralihan antar status. Sebaliknya, FSM hanya akan beroperasi ketika keadaan dari FSM pertama adalah "01", dan kemudian FSM ini akan bertransisi antar keadaan hanya pada tepi naik dari sinyal clock. Perbedaan lainnya adalah modul ini memiliki logika keluaran, artinya modul ini tidak menampilkan status saat ini, melainkan mengeluarkan bilangan biner untuk nada pada status tersebut.

Masukan

- Clk_BPM (sinyal jam BPM dari pembagi jam)

- FSM1_state (PS dari PPS FSM)

- Pitch_in (nada dari note_assign)

Keluaran

Pitch_out (satu nada pada satu waktu, untuk output_select dan seg_display)

Komponen

- MUX

- D mendaftar

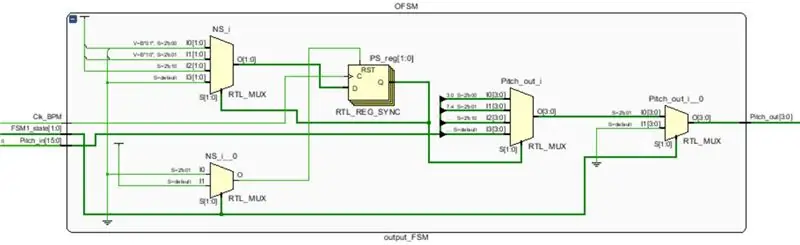

Langkah 10: Keluarkan FSM

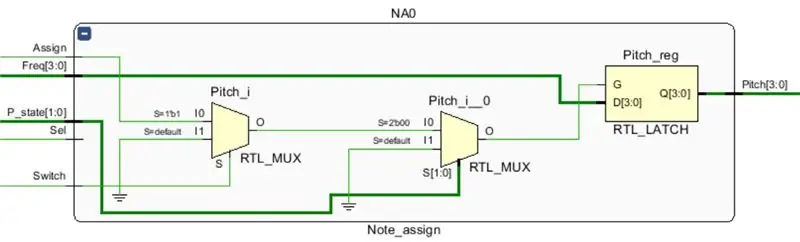

Langkah 11: Catatan Tugas

Modul penetapan not bertanggung jawab untuk benar-benar menetapkan nada ke not posisi, atau langkah. Modul ini sebenarnya cukup sederhana. Ini pertama-tama memeriksa apakah sirkuit dalam keadaan "seleksi" dan apakah sakelar langkah (paling kiri) tinggi. Jika ini benar dan tombol penetapan ditekan, keluaran modul akan sama dengan bilangan biner yang diwakili oleh sakelar frekuensi (paling kanan).

Awalnya, kami telah mencoba membuat modul yang benar-benar akan menyimpan salah satu sinyal jam pitch ke output, tetapi kami mengalami masalah dengan perubahan output untuk mengikuti sinyal jam input. Ini adalah satu-satunya modul yang digunakan lebih dari sekali dalam desain akhir. Setiap langkah memiliki modul note_assign yang terkait dengannya, dan karena itu, setiap instance modul mendapat satu bit bus Langkah.

Masukan

- P_state (keadaan sekarang dari PPS FSM)

- Sel (tombol kiri)

- Saklar (saklar satu langkah)

- Freq (saklar paling kanan untuk nada)

- Tetapkan (tombol bawah, berikan catatan)

Keluaran

Pitch (bilangan biner, ke output_FSM)

Komponen

- MUX

- D mendaftar

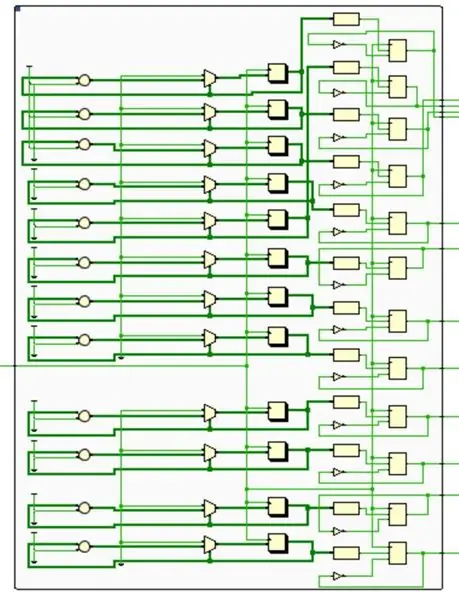

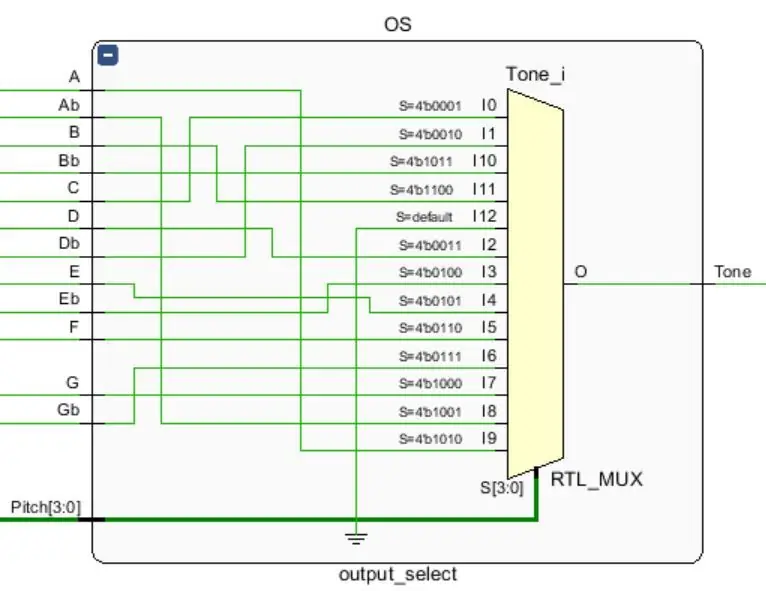

Langkah 12: Pilih Output

Output select bertanggung jawab untuk mengambil nomor biner untuk pitch dan menghubungkannya ke sinyal clock masing-masing. Terlepas dari ukurannya, ini juga merupakan modul yang relatif sederhana. Output_select pada dasarnya adalah dekoder biner, mendekode angka biner untuk nada ke sinyal jam tertentu. Sebenarnya menetapkan output ke frekuensi clock bekerja lebih baik di sini dibandingkan dengan modul note_assign, karena semua modul ini harus lakukan adalah MUX sinyal clock dengan angka biner yang mewakili input kontrol.

Kami mohon maaf atas perutean yang aneh, Vivado mengatur sinyal nada menurut abjad untuk file clk_div_pitches, tetapi untuk file ini ia mengaturnya dengan menaik angka biner, menyebabkan nada berada dalam urutan yang berbeda. Perhatikan juga bahwa jika bilangan biner dari output_FSM adalah "0000" atau lebih besar dari "1100", maka MUX dikirim melalui sinyal datar '0'.

Memasukkan

- Pitch (dari output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (sinyal pitch clock)

Keluaran

Nada (satu bit yang cocok dengan sinyal clock yang dipilih, ke square_wave)

Komponen

MUX

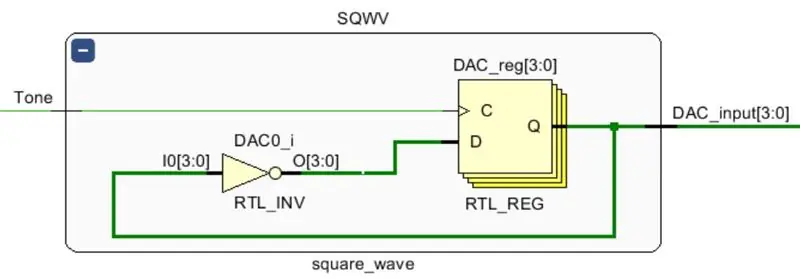

Langkah 13: Gen Gelombang Persegi

Modul square_wave adalah generator untuk gelombang persegi yang dikeluarkan dari board ke DAC. Menggunakan sinyal nada dari file sebelumnya, square_wave ini membalikkan angka 4 bit antara "0000" dan "1111" pada tepi naik Nada. Nada adalah frekuensi nada tertentu, jadi square_wave menghasilkan gelombang dengan frekuensi yang berbeda ketika output_FSM bertransisi ke keadaan lain. Output 4-bit dari modul ini menuju ke modul fin_sel, di mana logika menentukan apakah bus ini akan dikeluarkan berdasarkan status dari PPS FSM.

Alternatif untuk generator gelombang persegi ini adalah menghasilkan gelombang sinus. Meskipun ini kemungkinan besar akan menghasilkan nada akhir yang lebih baik, ini jauh lebih sulit untuk diterapkan, jadi kami memilih untuk hanya menghasilkan gelombang persegi.

Masukan

Nada (bit berosilasi dari output_select)

Keluaran

DAC_input (bus 4-bit berosilasi yang berubah pada frekuensi nada yang sama)

Komponen

- Inverter

- D daftar

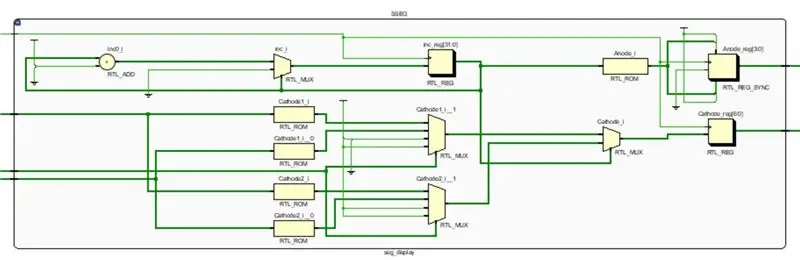

Langkah 14: Tampilan 7-segmen

Modul seg_display mengontrol tampilan 7-segmen pada papan basys kami. Dalam modul, dua proses terjadi. Proses pertama menerjemahkan Freq saat dalam status "seleksi" atau Pitch saat dalam mode "putar". Dalam mode "jeda", modul diterjemahkan untuk menampilkan simbol jeda. Melihat kode VHDL, Anda dapat melihat bahwa dekoder biner sebenarnya menerjemahkan input menjadi dua sinyal yang berbeda, katoda1 dan katoda2. Katoda1 mewakili huruf yang sesuai dengan nada yang akan ditampilkan, dan katoda2 mewakili simbol datar (b) jika ada. Alasan untuk ini berkaitan dengan proses kedua yang dilakukan oleh modul seg_display.

Pada papan basys3, tampilan segmen memiliki katoda umum. Sementara anoda mengontrol digit mana yang dihidupkan, katoda mengontrol segmen mana yang menyala. Karena layar memiliki katoda umum, itu berarti Anda hanya dapat menampilkan satu set segmen pada satu waktu. Itu menimbulkan masalah untuk proyek ini karena kami ingin menampilkan huruf pada digit pertama dan simbol datar, jika perlu, pada saat yang bersamaan. Sekarang ingat sinyal jam 7seg? Untuk mengatasi masalah ini, kami mengubah anoda dan katoda bolak-balik pada sinyal jam 7seg. Karena sinyal clock adalah 240 Hz dan kami menggunakan dua digit, setiap digit akan berosilasi pada 60 Hz. Untuk mata manusia, itu akan terlihat seperti angka yang tidak berosilasi sama sekali.

Perhatikan juga bahwa tampilan papan basys3 menggunakan logika negatif. Ini berarti jika anoda atau katoda diatur ke '0', digit atau segmen itu akan aktif, dan sebaliknya.

Masukan

- Pitch (nomor biner untuk not, digunakan dalam status putar)

- Freq (saklar frekuensi, digunakan saat dalam keadaan pemilihan)

- P_state (status sekarang dari PPS FSM)

- Clk_240Hz (sinyal clock dari Clk_div_7seg, double 120 karena kami hanya menggunakan tepi naik)

Keluaran

- Katoda (bus yang mengontrol segmen pada tampilan, keluaran akhir)

- Anoda (bus yang mengontrol angka pada tampilan, keluaran akhir)

Komponen

- Memalangi

- MUX

- D mendaftar

Langkah 15: Pilihan Terakhir

Pilihan terakhir adalah modul terakhir yang digunakan dalam proyek ini. Modul sederhana lainnya, modul ini mengontrol output akhir yang akan masuk ke DAC. Saat dalam status "seleksi" atau "jeda", modul akan mengeluarkan "0000" statis sehingga tidak ada musik yang dimainkan dari speaker. Dalam status "play", modul akan menampilkan 4-bit berosilasi seperti yang ditentukan oleh square_wave.

Masukan

- P_state (status sekarang dari PPS FSM)

- DAC_input (osilasi 4-bit dari square_wave)

Keluaran

DAC (sama dengan DAC_input dalam status putar, keluaran akhir)

Komponen

MUX

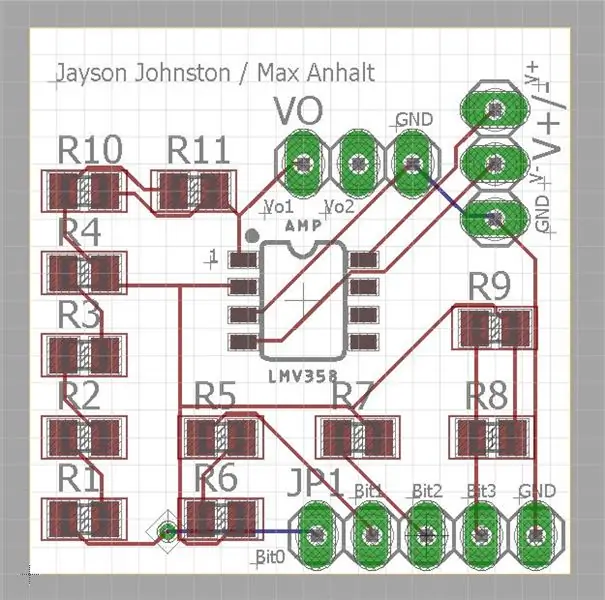

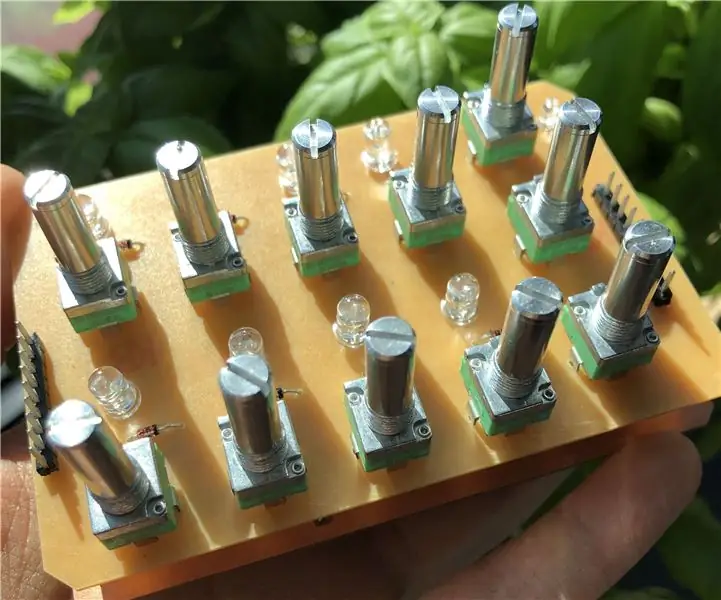

Langkah 16: Perangkat Eksternal: DAC

Konverter digital ke analog (DAC) mengambil sinyal diskrit dan mengubahnya menjadi sinyal kontinu. DAC kami memiliki empat bit dan terbuat dari penguat penjumlahan. Dengan menggunakan rasio resistor dalam loop suplai dan umpan balik, kami dapat membuat sistem yang menghasilkan 16 level berbeda yang dibuat oleh "penjumlahan" setiap cabang. Bit0, cabang teratas, membawa bobot paling sedikit dan memberikan kontribusi potensi terkecil saat tinggi karena cabang itu memiliki resistensi yang lebih tinggi. Beratnya bertambah saat Anda menuruni cabang. Jika Anda menghitung dalam biner ke atas dan kemudian mundur menggunakan input bit, tegangan output akan terlihat seperti gelombang sinus langkah bijaksana. Input ke DAC terhubung ke salah satu PMOD di papan untuk mentransfer sinyal 4-bit.

DAC awalnya dirakit untuk kelas Teknik Elektro dan dirancang dan disolder oleh kami, tidak dibeli dari toko. Di atas adalah gambar dari file desain untuk membuat papan sirkuit tercetak.

Langkah 17: Perangkat Eksternal: Speaker

Untuk proyek ini, Anda tidak akan ingin membeli sepasang speaker yang sangat bagus. Seperti yang Anda tahu, suaranya cukup mendasar. Kami pergi dan membeli satu set speaker komputer seharga $8 dari Best Buy. Apa pun dengan jack headphone berfungsi dengan baik. Monoton juga berfungsi dengan baik. Anda bahkan dapat menggunakan headphone, tetapi Anda mungkin akan meledakkannya!

Untuk menghubungkan output DAC ke speaker, kami menggunakan kabel jumper dan kemudian menahan kabel output ke ujung jack headphone dan kabel ground ke pangkalan. Kami mencoba menggunakan pita listrik untuk menahan kabel di tempatnya, tetapi itu menyebabkan banyak gangguan. Mencoba gaya pita yang berbeda dapat mengatasi masalah ini.

Untuk speaker kami, kami mengubahnya ke pengaturan tertinggi dan mendapatkan suara yang cukup keras.

Dan itu adalah langkah terakhir untuk membuat sequencer digital dari papan FPGA! Buka dua bagian berikutnya untuk mengunduh semua kode VHDL kami dan melihat sequencer beraksi.

Langkah 18: Demo Video

Video ini menunjukkan versi final dari proyek kerja, termasuk proses menetapkan sakelar ke 4 nada berbeda, dan pembicara memainkan nada masing-masing.

Langkah 19: Kode VHDL

Berikut adalah kode untuk keseluruhan proyek, termasuk kendala dan file sim yang digunakan saat membangun sequencer. Perhatikan bahwa file desain yang tidak digunakan mengatakan demikian dalam arsitektur.

Direkomendasikan:

Arduino MIDI Rhythm Section Sequencer: 8 Langkah (dengan Gambar)

Arduino MIDI Rhythm Section Sequencer: Memiliki mesin drum perangkat lunak yang bagus mudah dan murah hari ini tetapi menggunakan mouse membunuh kesenangan bagi saya. Inilah mengapa saya menyadari apa yang awalnya dimaksudkan sebagai perangkat keras 64 langkah MIDI drum sequencer murni yang mampu memicu hingga 12 elemen drum yang berbeda

Synth Sequencer Paralel: 17 Langkah (dengan Gambar)

Parallel Sequencer Synth: Ini adalah panduan untuk membuat sequencer sederhana. Sequencer adalah perangkat yang secara siklis menghasilkan serangkaian langkah yang kemudian menggerakkan osilator. Setiap langkah dapat ditetapkan ke nada yang berbeda dan dengan demikian menciptakan urutan atau efek audio yang menarik

Simple Sequencer: 16 Langkah (dengan Gambar)

Simple Sequencer: Salah satu kunci untuk membuat musik yang bagus adalah pengulangan tanpa berpikir. Itulah keunggulan sequencer sederhana. Itu melakukan hal yang sama berulang-ulang dalam urutan delapan nada. Anda dapat menyesuaikan frekuensi nada, durasi nada, dan

Atari Punk Console Dengan Baby 8 Step Sequencer: 7 Langkah (dengan Gambar)

Atari Punk Console Dengan Baby 8 Step Sequencer: Build perantara ini adalah All-in-one Atari Punk Console dan Baby 8 Step Sequencer yang dapat Anda giling di Mesin Penggilingan PCB Desktop Bantam Tools. Ini terdiri dari dua papan sirkuit: satu adalah papan antarmuka pengguna (UI) dan yang lainnya adalah

(hampir) Universal MIDI SysEx CC Programmer (dan Sequencer): 7 Langkah (dengan Gambar)

(hampir) Universal MIDI SysEx CC Programmer (dan Sequencer…): Pada pertengahan tahun delapan puluhan pabrikan synth memulai "kurang lebih baik" proses yang mengarah ke barebone synths. Ini memungkinkan pengurangan biaya di sisi pabrikan, tetapi membuat proses penambalan menjadi membosankan jika bukan tidak mungkin untuk penggunaan akhir