Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:56.

- Terakhir diubah 2025-01-23 14:49.

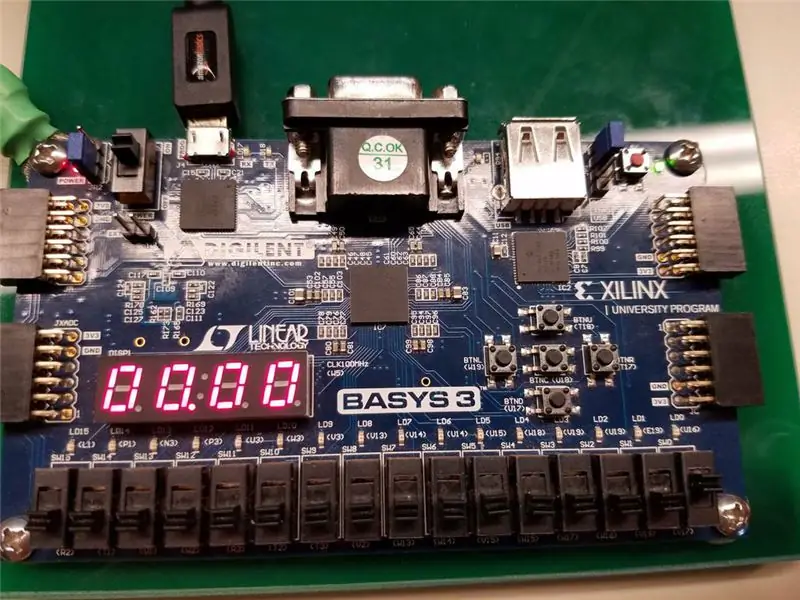

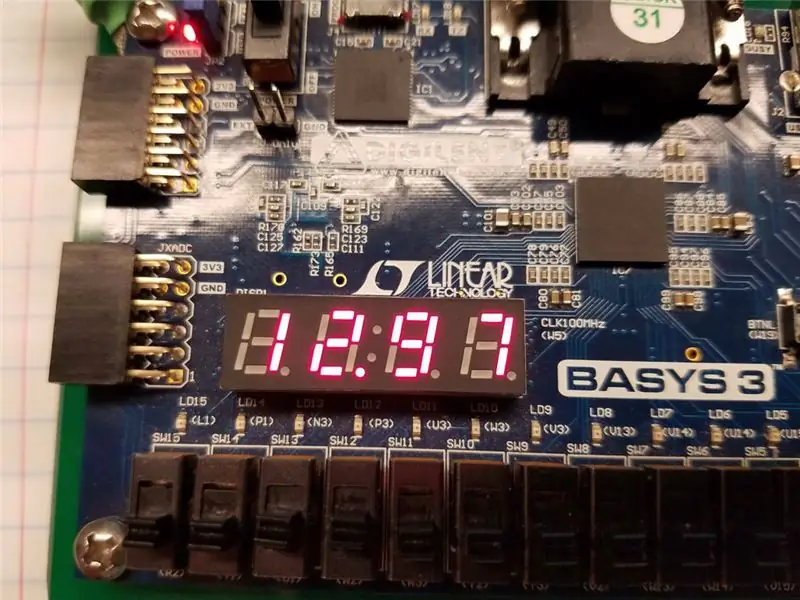

Selamat datang di instruksi tentang cara membuat stopwatch menggunakan papan VHDL dan Basys 3 dasar. Kami sangat senang untuk berbagi proyek kami dengan Anda! Ini adalah tugas akhir untuk kursus CPE 133 (Desain Digital) di Cal Poly, SLO pada Musim Gugur 2016. Proyek yang kami buat adalah stopwatch sederhana yang memulai, mengatur ulang, dan menjeda waktu. Dibutuhkan tiga tombol tekan pada papan Basys3 sebagai input, dan waktu ditampilkan pada layar tujuh segmen empat digit papan. Waktu yang telah berlalu ditampilkan dalam format detik: centiseconds. Ini menggunakan jam sistem papan sebagai input untuk melacak waktu yang telah berlalu dan mengeluarkan waktu ke empat digit dari tampilan tujuh segmen.

Langkah 1: Bahan

Bahan yang Anda perlukan untuk proyek ini:

- 1 komputer dengan Vivado Design Suite WebPack diinstal dari Xilinx (lebih suka versi 2016.2)

- 1 papan Digilent Basys3 Xilinx Artix-7 FPGA

- 1 kabel port USB

Langkah 2: Mengatur Input dan Output

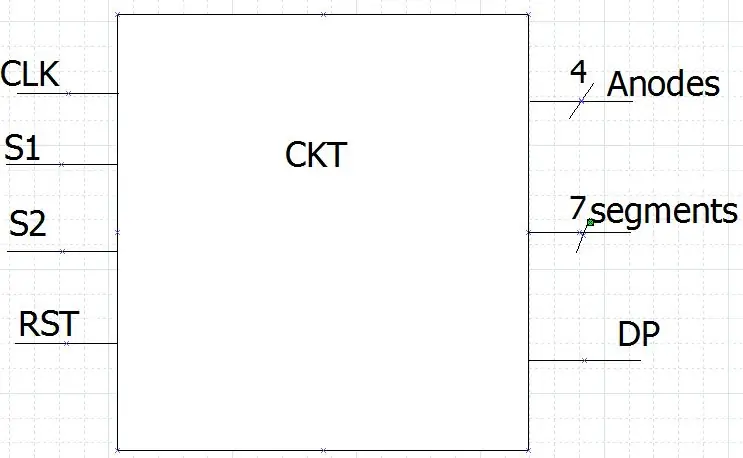

Gambar di atas menunjukkan diagram blok tingkat atas dari modul stopwatch utama. Stopwatch menerima input "CLK" (jam), "S1" (tombol mulai), "S2" (tombol jeda), dan "RST" (reset) dan memiliki output 4-bit "Anoda", 7-bit keluaran "segmen", dan keluaran bit tunggal "DP" (titik desimal). Ketika input "S1" tinggi, stopwatch mulai menghitung waktu. Saat "S2" rendah, stopwatch menjeda waktu. Ketika "RST" tinggi, stopwatch berhenti dan mengatur ulang waktu. Ada empat submodul dalam rangkaian: pembagi jam, penghitung angka, driver tampilan tujuh segmen, dan enkoder tampilan tujuh segmen. Modul utama stopwatch menghubungkan semua submodul bersama-sama dan ke input dan output.

Langkah 3: Membuat Jam

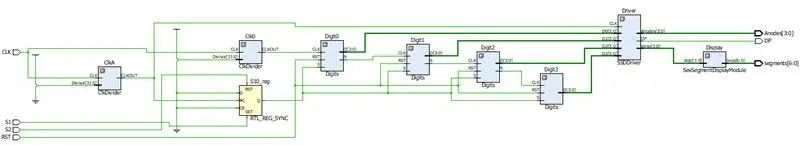

Modul pembagi jam mengambil jam sistem dan menggunakan input pembagi untuk membuat jam dengan kecepatan apa pun yang tidak lebih besar dari jam sistem. Stopwatch menggunakan dua modul jam yang berbeda, satu yang menghasilkan jam 500 Hz dan yang lainnya menghasilkan jam 100 Hz. Skema untuk jam pembagi ditunjukkan pada gambar di atas. Pembagi jam menerima input bit tunggal "CLK", dan input 32-bit "Pembagi" dan output bit tunggal "CLKOUT". "CLK" adalah jam sistem dan "CLKOUT" adalah jam yang dihasilkan. Modul ini juga menyertakan gerbang NOT, yang mengaktifkan sinyal "CLKTOG" ketika hitungan mencapai nilai pembagi.

Langkah 4: Menghitung sampai Sepuluh

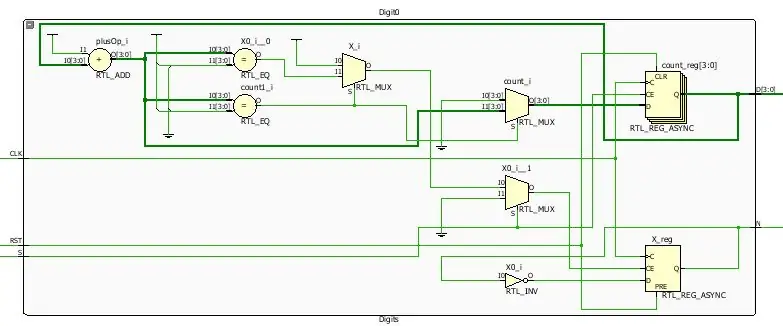

Penghitung digit menghitung setiap digit dari 0 hingga 10 dan membuat jam lain untuk digit berikutnya agar berfungsi dari yang berosilasi ketika hitungan mencapai 10. Modul menerima 3 input bit tunggal "S", "RST", dan "CLK " dan menghasilkan keluaran bit tunggal "N" dan keluaran 4 bit "D". Input "S" adalah aktifkan input. Jam menyala saat "S" tinggi dan mati saat "S" rendah. "RST" adalah input reset sehingga jam disetel ulang ketika "RST" tinggi. "CLK" adalah input jam untuk penghitung angka. "N" adalah output jam yang menjadi jam input untuk digit berikutnya. Output "D" menyajikan nilai biner dari digit penghitung.

Langkah 5: Menampilkan Angka

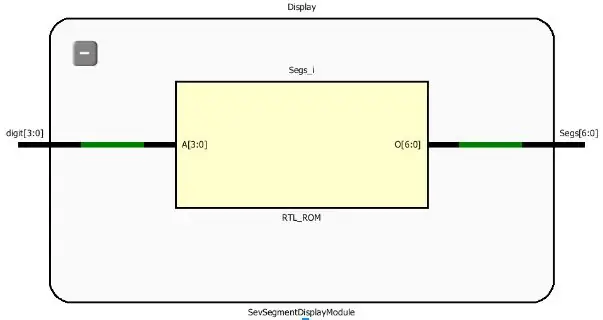

Encoder tampilan tujuh segmen akan mengkodekan angka biner yang diterima dari modul driver tampilan tujuh segmen dan mengubahnya menjadi aliran bit yang akan ditafsirkan sebagai nilai '1' atau '0' untuk setiap segmen tampilan. Angka biner diterima oleh modul sebagai "digit" input 4-bit dan menghasilkan "segmen" output 7-bit. Modul ini terdiri dari blok proses kasus tunggal yang menetapkan aliran 7-bit spesifik untuk setiap nilai input yang mungkin dari 0 hingga 9. Setiap bit dalam aliran tujuh-bit mewakili salah satu dari tujuh segmen digit pada tampilan. Urutan segmen dalam aliran adalah "abcdefg" dengan '0 mewakili segmen yang menyala untuk nomor yang diberikan.

Langkah 6: Cara Menampilkan Stopwatch

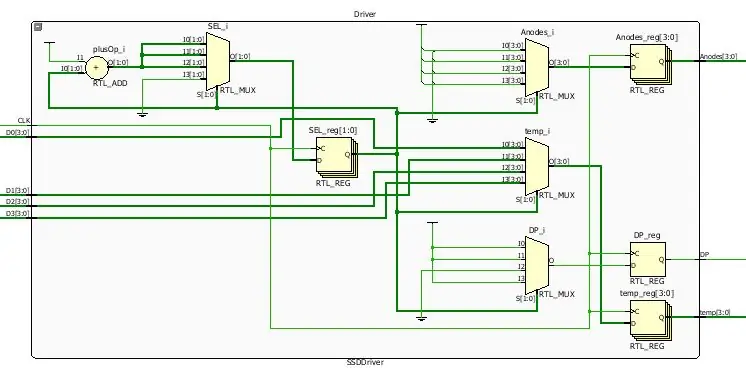

Dalam modul driver tampilan tujuh segmen, ada empat input 4-bit "D0", "D1", "D2", dan "D3", masing-masing mewakili empat digit yang akan ditampilkan. Input "CLK" adalah input jam dari sistem. Output bit tunggal "DP" mewakili titik desimal pada tampilan tujuh segmen. Output 4-bit "Anoda" menentukan digit mana pada tampilan tujuh segmen yang ditampilkan dan "temp" output 4-bit tergantung pada status input kontrol 2-bit "SEL". Modul ini menggunakan 4 multiplexer untuk input kontrol "SEL" dan tiga output; "Anoda", "suhu", dan "DP".

Langkah 7: Menyatukan Semuanya

Blok proses 'jika' yang berjalan pada jam 500Hz digunakan untuk membuat tombol mulai dan jeda. Kemudian hubungkan semua submodul bersama-sama dalam modul utama stopwatch dengan mendeklarasikan komponen masing-masing submodul dan menggunakan berbagai sinyal. Submodul digit mengambil output jam dari submodul digit sebelumnya dengan yang pertama mengambil jam 100Hz. Output "D" dari submodul digit kemudian menjadi input "D" dari modul driver tampilan tujuh segmen. Dan terakhir output "temp" dari modul driver tampilan tujuh segmen menjadi input "temp" dari modul encoder tujuh segmen.

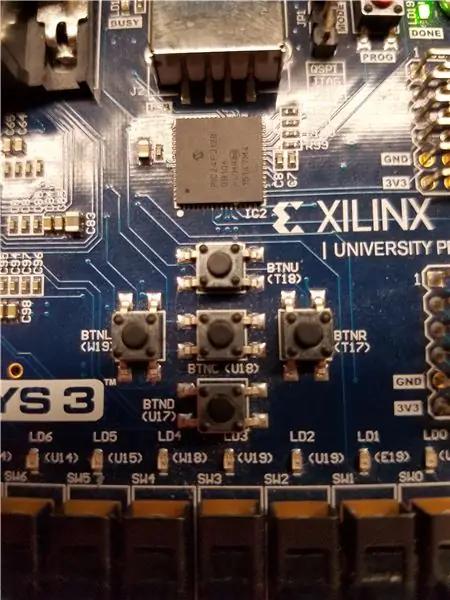

Langkah 8: Kendala

Gunakan 3 tombol push (W19, T17, dan U18) untuk input "RST", "S1", dan "S2". W19 adalah tombol reset, T17 adalah tombol start (S1), dan U18 adalah tombol pause (S2). Batasan untuk input input clock juga diperlukan menggunakan port W5. Juga, ingatlah untuk menambahkan baris ini ke batasan jam:

create_clock -tambahkan -nama sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Juga hubungkan Anoda dan segmen ke papan sehingga stopwatch ditampilkan pada tampilan tujuh segmen seperti yang terlihat pada file kendala.

Langkah 9: Pengujian

Pastikan perangkat Anda berfungsi dengan memainkan tiga tombol: menekan dan menahannya dalam setiap urutan yang memungkinkan untuk menemukan kemungkinan masalah dengan kode Anda.

Direkomendasikan:

Menggunakan Fluks - Dasar-dasar Solder: 5 Langkah

Menggunakan Fluks | Dasar-dasar Solder: Setiap kali Anda menyolder, solder perlu membuat ikatan yang baik dengan bagian-bagian yang Anda solder. Logam bagian dan logam solder harus bersentuhan langsung satu sama lain untuk menciptakan ikatan yang baik. Tapi karena saya

Dasar-dasar VBScript - Memulai Skrip Anda, Penundaan, dan Lainnya!: 5 Langkah

Dasar-Dasar VBScript - Memulai Skrip, Penundaan, dan Lainnya!: Selamat datang di tutorial pertama saya tentang cara membuat VBScript dengan notepad. Dengan file .vbs, Anda dapat membuat beberapa lelucon lucu atau virus mematikan. Dalam tutorial ini, saya akan menunjukkan perintah dasar seperti memulai skrip, membuka file, dan banyak lagi. Di t

Cara Mengontrol Perangkat Menggunakan Raspberry Pi dan Relay - DASAR-DASAR: 6 Langkah

Cara Mengontrol Perangkat Menggunakan Raspberry Pi dan Relay - DASAR-DASAR: Ini adalah tutorial dasar dan langsung tentang cara mengontrol perangkat menggunakan Raspberry Pi dan Relay, membantu untuk membuat Proyek IoTTutorial ini untuk pemula, ramah untuk ikuti terus bahkan jika Anda tidak memiliki pengetahuan tentang penggunaan Raspberry

Dasar-dasar IoT: Menghubungkan IoT Anda ke Cloud Menggunakan Mongoose OS: 5 Langkah

Dasar-dasar IoT: Menghubungkan IoT Anda ke Cloud Menggunakan Mongoose OS: Jika Anda adalah orang yang suka mengutak-atik dan elektronik, lebih sering daripada tidak, Anda akan menemukan istilah Internet of Things, biasanya disingkat IoT, dan itu mengacu pada satu set perangkat yang dapat terhubung ke internet! Menjadi orang seperti itu

Cara Menggunakan Dasar-dasar Multimeter: 8 Langkah

Cara Menggunakan Multimeter Dasar: Multimeter atau multitester, juga dikenal sebagai VOM (volt-ohm-milliammeter), adalah alat ukur elektronik yang menggabungkan beberapa fungsi pengukuran dalam satu unit. Multimeter tipikal dapat mengukur tegangan, arus, dan hambatan. Multi analog