Daftar Isi:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 09:54.

- Terakhir diubah 2025-01-23 14:49.

Dalam Instruksi ini kami akan menjelaskan cara menerapkan konverter analog-ke-digital (ADC) 8-bit di SLG46855V yang dapat merasakan arus beban dan antarmuka dengan MCU melalui I2C. Desain ini dapat digunakan untuk berbagai aplikasi penginderaan arus seperti amperemeter, sistem deteksi kesalahan, dan pengukur bahan bakar.

Di bawah ini kami menjelaskan langkah-langkah yang diperlukan untuk memahami bagaimana solusi telah diprogram untuk menciptakan pengertian arus ADC. Namun, jika Anda hanya ingin mendapatkan hasil pemrograman, unduh perangkat lunak GreenPAK untuk melihat File Desain GreenPAK yang sudah selesai. Colokkan GreenPAK Development Kit ke komputer Anda dan tekan program untuk menciptakan pengertian arus ADC.

Langkah 1: Arsitektur ADC

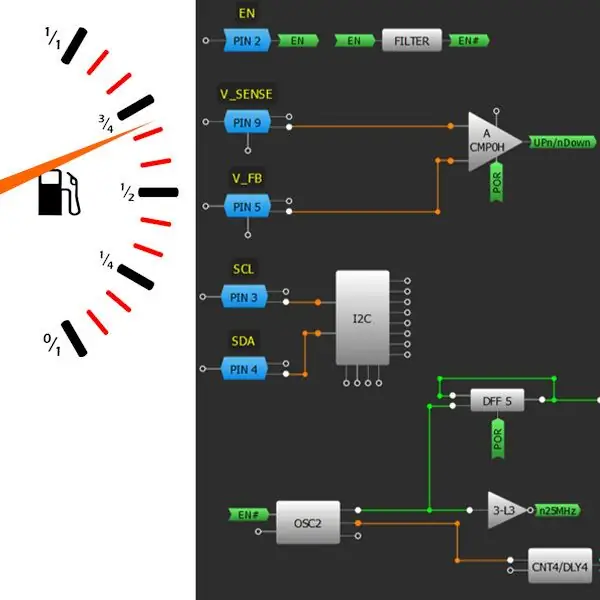

ADC pada dasarnya terdiri dari pembanding analog dan Digital-to-Analog Converter (DAC). Komparator merasakan tegangan input vs tegangan output DAC, dan selanjutnya mengontrol apakah akan menambah atau mengurangi kode input DAC, sehingga output DAC menyatu dengan tegangan input. Kode input DAC yang dihasilkan menjadi kode output digital ADC.

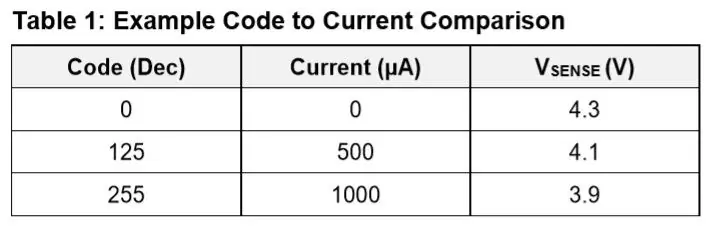

Dalam implementasi kami, kami membuat DAC menggunakan jaringan resistor terkontrol modulasi lebar-pulsa (PWM). Kita dapat dengan mudah membuat output PWM yang dikontrol secara digital menggunakan GreenPAK. PWM ketika disaring menjadi tegangan analog kami dan dengan demikian berfungsi sebagai DAC yang efektif. Keuntungan yang berbeda dari pendekatan ini adalah mudah untuk mengatur tegangan yang sesuai dengan kode nol dan skala penuh (setara offset dan gain) hanya dengan menyesuaikan nilai resistor. Misalnya, pengguna ingin membaca kode nol secara ideal dari sensor suhu tanpa arus (0 A) yang sesuai dengan 4,3 V, dan kode skala penuh pada 1000 A yang sesuai dengan 3,9 V (Tabel 1). Ini mudah diimplementasikan hanya dengan mengatur beberapa nilai resistor. Dengan memiliki rentang ADC yang sesuai dengan rentang sensor yang diinginkan, kami memanfaatkan resolusi ADC secara maksimal.

Pertimbangan desain untuk arsitektur ini adalah bahwa frekuensi PWM internal harus jauh lebih cepat daripada kecepatan pembaruan ADC untuk mencegah perilaku loop kontrol yang kurang teredam. Setidaknya harus lebih lama dari jam penghitung data ADC dibagi 256. Dalam desain ini, periode pembaruan ADC diatur ke 1,3312 ms.

Langkah 2: Sirkuit Internal

ADC fleksibel didasarkan pada desain yang disajikan dalam Dialog Semiconductor AN-1177. Kecepatan clock ditingkatkan dari 1 MHz menjadi 12,5 MHz untuk melakukan clock counter ADC karena SLG46855 memiliki clock 25 MHz yang tersedia. Ini memungkinkan tingkat pembaruan yang jauh lebih cepat untuk resolusi sampel yang lebih baik. Clocking LUT clock data ADC diubah sehingga akan melewati sinyal 12,5 MHz saat PWM DFF rendah.

Langkah 3: Sirkuit Eksternal

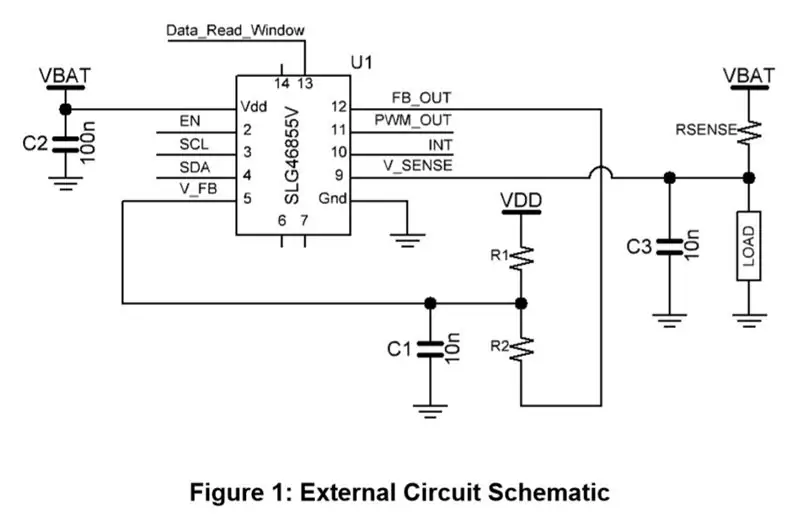

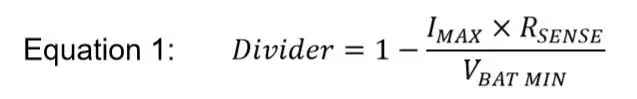

Sebuah resistor eksternal dan jaringan kapasitor digunakan untuk mengubah PWM menjadi tegangan analog seperti yang ditunjukkan pada skema rangkaian pada Gambar 1. Nilai dihitung untuk resolusi maksimum untuk arus maksimum yang akan dirasakan perangkat. Untuk mencapai fleksibilitas ini, kami menambahkan resistor R1 dan R2 secara paralel ke VDD dan ground. Sebuah pembagi resistor membagi VBAT ke sisi rendah dari rentang tegangan. Rasio pembagi untuk VBAT minimum yang diharapkan dapat diselesaikan dengan menggunakan persamaan 1.

Langkah 4: I2C Baca Instruksi

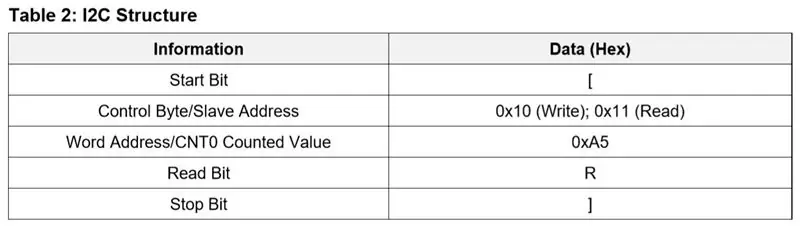

Tabel 1 menjelaskan struktur perintah I2C untuk membaca kembali data yang disimpan di CNT0. Perintah I2C membutuhkan start bit, control byte, word address, read bit, dan stop bit.

Contoh perintah I2C untuk membaca kembali nilai terhitung CNT0 ditulis di bawah ini:

[0x10 0xA5] [0x11 R]

Nilai terhitung yang dibaca kembali akan menjadi nilai kode ADC. Sebagai contoh, kode Arduino disertakan dalam file ZIP dari catatan aplikasi ini di situs web Dialog.

Langkah 5: Hasil

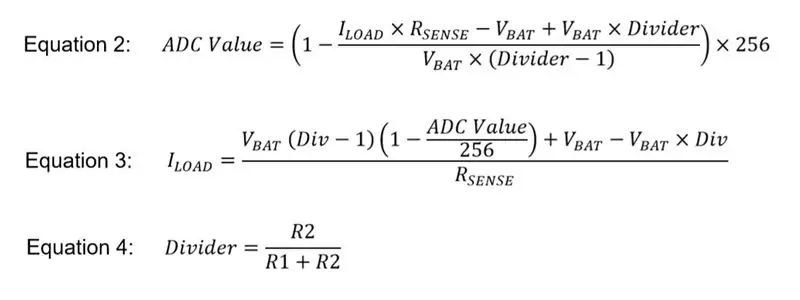

Untuk menguji keakuratan desain sensor arus ADC, nilai terukur pada arus beban dan tingkat VDD yang diberikan dibandingkan dengan nilai teoretis. Nilai ADC teoritis dihitung dengan persamaan 2.

ILOAD yang berkorelasi dengan nilai ADC ditemukan dengan persamaan 3.

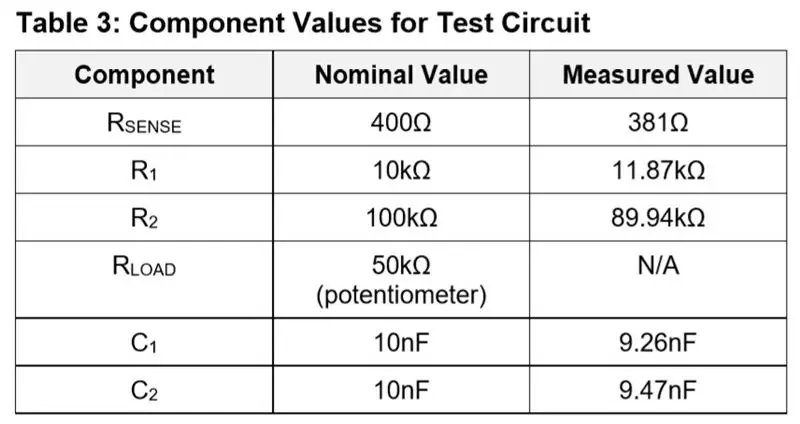

Untuk hasil berikut saya menggunakan nilai komponen ini yang ditunjukkan pada Tabel 3.

Resolusi konversi nilai ADC ke ILOAD dapat dihitung dengan menggunakan persamaan 3 dengan nilai terukur pada Tabel 2 dan nilai ADC diatur ke 1. Dengan VBAT 3,9 V resolusi 4,96 A/div.

Untuk mengoptimalkan rangkaian sensor arus ADC ke level VDD minimum 3,6 V dengan arus maksimum 1100 A dan resistor sensor 381, koefisien pembagi yang ideal adalah 0,884, berdasarkan persamaan 1. Dengan nilai yang diberikan pada Tabel 2, pembagi sebenarnya memiliki koefisien pembagi 0,876. Karena ini sedikit kurang, ini akan memungkinkan rentang arus beban yang sedikit lebih besar sehingga nilai ADC mendekati kisaran penuh tetapi tidak akan meluap. Nilai pembagi sebenarnya dihitung dengan persamaan 4.

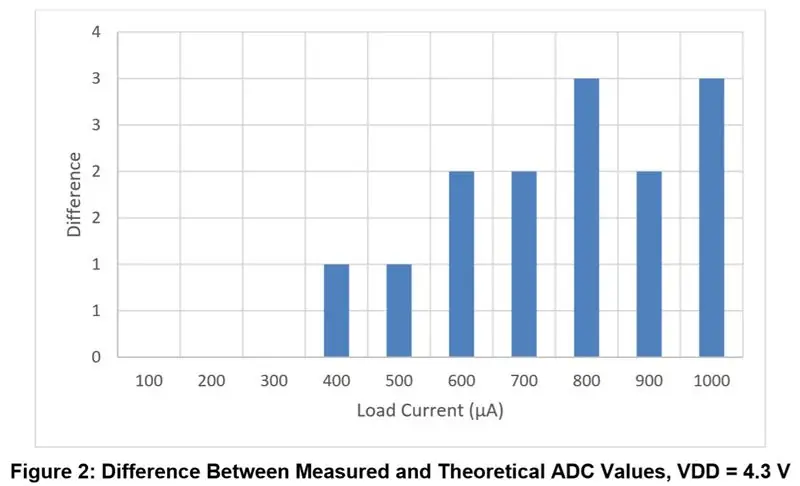

Di atas (Gambar 2-6, Tabel 4-6) adalah pengukuran yang dilakukan dari rangkaian pada tiga level tegangan: 4,3 V, 3,9 V, dan 3,6 V. Setiap level menampilkan grafik yang menampilkan perbedaan antara nilai ADC terukur dan teoretis. Nilai teoretis dibulatkan ke bilangan bulat terdekat. Ada grafik ringkasan untuk membandingkan perbedaan pada tiga level tegangan. Setelah itu ada grafik yang menampilkan korelasi antara nilai ADC teoritis dan arus beban pada level tegangan yang berbeda.

Kesimpulan

Perangkat diuji pada tiga level voltase: 3,6 V, 3,9 V, dan 4,3 V. Rentang voltase ini memodelkan baterai lithium ion penuh yang dilepaskan ke level nominalnya. Dari tiga level tegangan, diamati bahwa perangkat biasanya lebih akurat pada 3,9 V untuk rangkaian eksternal yang dipilih. Perbedaan antara nilai ADC terukur dan teoritis hanya turun 1 nilai desimal pada arus beban 700 - 1000 A. Pada rentang tegangan yang diberikan, nilai ADC yang diukur adalah 3 titik desimal di atas kondisi nominal pada kasus terburuk. Penyesuaian lebih lanjut pada pembagi resistor dapat dilakukan untuk mengoptimalkan level tegangan VDD yang berbeda.

Direkomendasikan:

Rotary Encoder - Memahami dan Menggunakannya (Arduino/Pengendali lainnya): 3 Langkah

Rotary Encoder - Memahami dan Menggunakannya (Arduino/otherPengendali lainnya): Rotary encoder adalah perangkat elektro-mekanis yang mengubah gerakan rotasi menjadi informasi digital atau analog. Itu bisa berputar searah jarum jam atau berlawanan arah jarum jam. Ada dua jenis enkoder putar: enkoder absolut dan relatif (tambahan).Wh

Cara Menghubungkan Aplikasi Android Dengan AWS IOT dan Memahami API Pengenalan Suara: 3 Langkah

Cara Menghubungkan Aplikasi Android Dengan AWS IOT dan Memahami API Pengenalan Suara: Tutorial ini mengajarkan pengguna cara menghubungkan Aplikasi Android ke server AWS IOT dan memahami API pengenalan suara yang mengontrol Mesin Kopi. Aplikasi mengontrol Mesin Kopi melalui Alexa Layanan Suara, setiap aplikasi

Memahami Elektronik 0 hingga 1 Dengan TinkerCAD: 5 Langkah

Memahami Elektronik 0 hingga 1 Dengan TinkerCAD: Memahami Elektronik dari nol tidak mudah, apa pun untuk Anak-anak atau orang dewasa. Sebagai Teknik Elektro profesional, saya dapat memahami betapa sulitnya Membuat Aturan Abstrak Realistis, sebelum Dapat Dimengerti. Saya akan menyarankan TinkerCAD terintegrasi MENYENANGKAN

Memahami Protokol IR Remote AC: 9 Langkah (dengan Gambar)

Memahami Protokol IR dari Remote AC: Saya telah belajar tentang protokol IR untuk beberapa waktu sekarang. Cara mengirim dan menerima sinyal IR. Pada titik ini, satu-satunya yang tersisa adalah protokol IR dari remote AC. Tidak seperti remote tradisional dari hampir semua perangkat elektronik (misalnya TV) di mana

Bagaimana Mengukur Arus dan Mengapa Harus Dilakukan?: 4 Langkah (dengan Gambar)

Bagaimana Mengukur Arus dan Mengapa Anda Harus Melakukannya?: Banyak pembuat tidak tahu betapa pentingnya mengetahui penarikan proyek Anda saat ini, atau mengapa Anda perlu mengetahuinya. Dalam tutorial ini saya akan menjelaskan kepada Anda bagaimana mengukur penarikan proyek Anda saat ini, dan mengapa sangat penting untuk mengetahui hal ini. T